プリント基板総合メーカー|RITAエレクトロニクス株式会社 > 技術資料 > 高速シリアル伝送対応設計の設計ガイドライン

高速シリアル伝送対応設計の設計ガイドライン

- 1. 高速シリアル伝送対応設計の3つの基本

高速シリアル伝送対応設計として、反射の抑制や伝送損失の低減、ノイズ抑制のために、

1.差動配線のインピーダンスコントロール、2.差動配線長の最短化、3.差動ペア内の配線長はできるだけそろえる、という3点を基本的なガイドラインとして基板設計を行います。

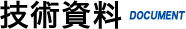

反射の抑制に関しては、前述の配線だけでなく、貫通穴(スルーホール)についても設計仕様を最適化することで、インピーダンスコントロールができ、デジタルコンシューマ機器でも普及しつつあります。コネクタについては実装部位の影響を考慮して最適化すること、またケーブルは実際の特性を十分に把握することが必須です。例えばコネクタの実装部位のパターン設計が適切でないと、多くの場合は余計な寄生容量が付いてインピーダンスが下がって反射し、伝送波形が悪くなるため、その部位の最適化が必要です。

また、高速シリアル伝送におけるシミュレーションの必要な領域に関しては、5Gbps以上と考えております。これは、5GbpsのPCI Expressの仕様書で、シミュレーションを用いたパターン設計段階での確認が必須と謳われている事、また、実際にトラブルを聞くことが多いためです。

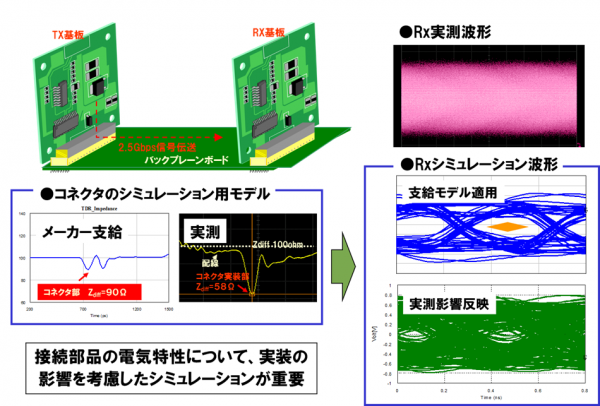

- 2. 高速シリアル伝送におけるリターンロス規格

高速シリアル伝送には、リターンロス、反射量の仕様のある規格が存在することがあります。

汎用的なインタフェースでは、ハードディスクSSD系のシリアルATA、放送やセキュリティーおよび画像医療の分野では、SDIが代表例です。

これらでは、半導体から外部入出力コネクタの間のパターン設計が合否を分けることになります。基板設計に関する技術が必要な領域です。例えば、シリアルATA用の表面実装コネクタの部位は寄生容量が大きくなりがちで、インピーダンスが下がり、特性が劣化します。

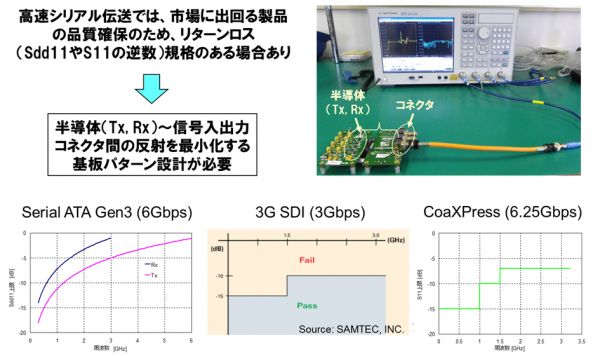

対策として、基板表層にある実装用パッド下のべたプレーンに一部抜きを設け、寄生容量を少なくする事で、配線の特性インピーダンスと同じにでき、特性が向上します。このような最適化を行うためには、ノウハウの蓄積も重要ですが、幅広いニーズに対応するためには、基板の設計情報から高精度に特性を抽出できるソフトウェアを利用することも手段としてはあります。

SDIインタフェースのBNCコネクタの実装用スルーホールを想定した検証例を図4に示します。抜きの大きさが2.3mm、3.5mm、4.5mmと大きくなるにつれて、特性インピーダンスが75Ωになっていく事実を良く再現できているのが分かります。

- 3. まとめ

高速シリアル伝送対応としては、差動配線のインピーダンスコントロール、差動配線長の最短化、差動ペア内の配線長はできるだけそろえる、という基本要素に加えて、貫通スルホールや実装部位の局所的なインピーダンスコントロールが重要となります。特に、リターンロス規格が存在するSDIインタフェースなどにおいては顕著であり、シミュレーションを活用した基板設計が必須と考えられます。

無料ダウンロード!

【ダウンロード資料例】

- DDR3メモリバスの設計手法

- 差動伝送路の設計と信号品質

- 12G-SDIリターンロス規格合致のための基板設計手法

- IBIS-AMIモデルを用いた高速信号シミュレーション

- 10Gbps超伝送の基板設計最適化

など全70テーマ

この機会に是非ご登録ください。 ※会員登録は無料です。