プリント基板総合メーカー|RITAエレクトロニクス株式会社 > 技術資料 > 高速メモリー搭載基板設計 IBISモデルの確度

高速メモリー搭載基板設計 IBISモデルの確度

1.IBISモデルの検証(HSPICEモデルとの比較)

高速メモリー搭載基板設計のシミュレーションには半導体のI/O部のシミュ レーションモデルであるIBISモデルが使用されます。IBISモデルはドライバーやレシーバーの動作を記述したものでビヘイビアモデルとなります。

一 方、高速信号伝送の解析にはHSPICEモデルを用いる場合もあります。HSPICEモデルは、半導体I/O部の回路設計情報を切り出し、エンクリプト (暗号化)したもので、回路情報がもととなっている事から確度は高いのですが、”シミュレーションに多大な時間を要す”,”取り扱い(信号の接続や与え 方)に統一性がなく困難”といった弱点があります。

また、半導体メーカーにとって機密性の高い情報である為、入手が難しい場合もあります。

上記よりDDR 系メモリーの波形シミュレーションにおいてIBISモデルが主流となります。本資料においては、IBISモデルがHSPICEモデルと同等の確度を示すか 否かを確認した内容を説明します。

対象としたのは、画像処理用のASSPです。2.IBISモデル vs HSPICEモデル 比較結果

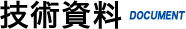

図1に比較内容一覧を記載しました。以下はその結果となります。

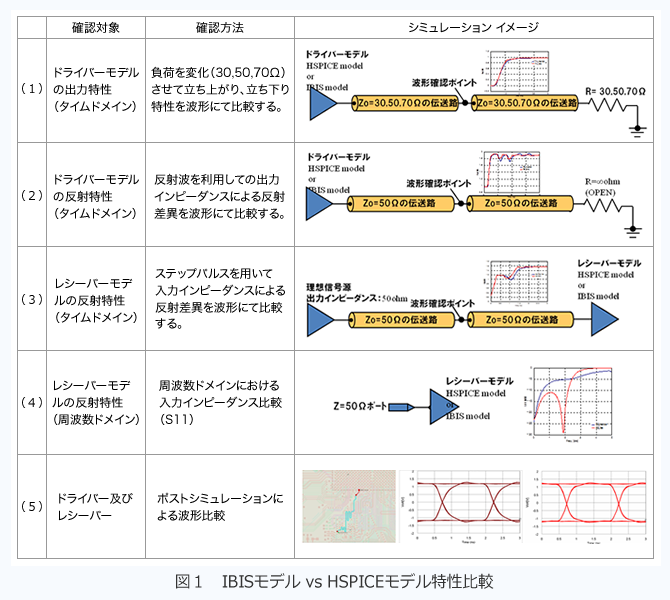

(1)負荷を変化させてのドライバーモデルの出力特性比較(図2)

- 全体的に立ち上り(立ち下り)波形にほとんど差は無い。

- IBISモデルの立ち上り(立ち下り)の方がやや急峻である。

- IBISでは既定電位に到達する前に波形がひずむ。容量が2箇所に分散しているため(C_compとpkg)と考えられ、HSPICEに比べ、精度はやや劣るが、概ねシミュレーションには影響の無いレベルである。

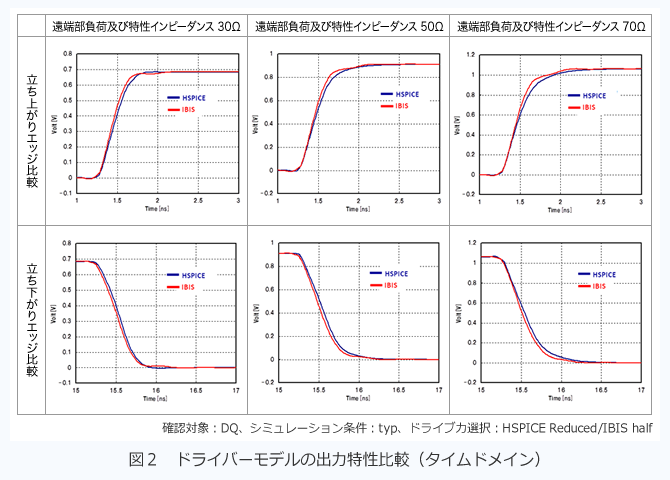

(2)ドライバーの反射特性比較(図3)

- インピーダンスの挙動について、DC的にはReduced / half が約50Ω,Increase / IBIS:fullが約30Ω程度でHSPICEとIBISには差異は無い。

- AC的にはIBISはHSPICEと比べ、インピーダンスの変動に滑らかさが少ない。(パッケージやCcompを集中定数として分散している事が要因)

- 強くリンギングが発生する伝送系でのシミュレーションでは、IBISはHSPICEに比べやや確度が劣るが、インピーダンスマッチングを考慮した伝送系では、実運用上問題はない。

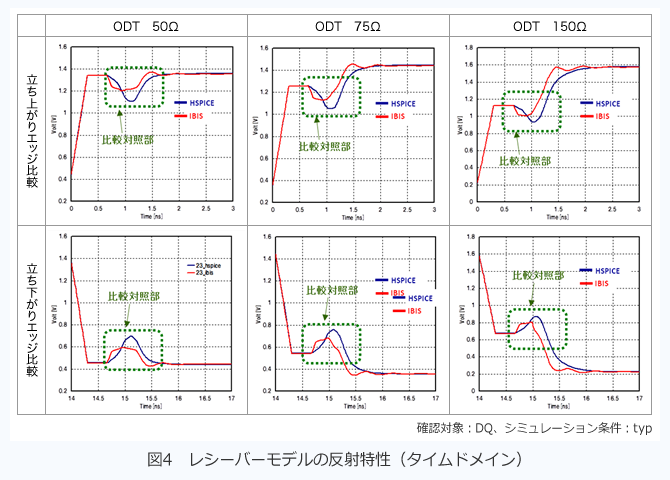

(3)レシーバーモデルの反射特性比較(タイムドメイン)(図4)

インピーダンスの挙動について、DC的にはHSPICEとIBISには差異は無い。

AC的にはドライバー同様IBISはHSPICEと比べ、インピーダンスの変動に滑らかさが少ない。 (パッケージやCcompを集中定数として分散している事が要因)

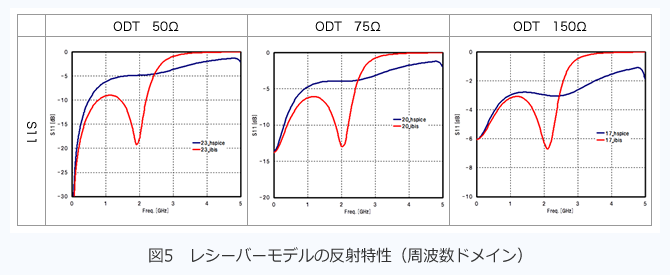

強くリンギングが発生する伝送系でのシミュレーションでは、IBISはHSPICEに比べやや確度が劣るが、インピーダンスマッチングを考慮した伝送系では、実運用上問題はない。(4)レシーバーモデルの反射特性比較(周波数ドメイン)(図5)

333MHzの3次高調波である1GHz以下では、IBISの反射特性はHSPICEと概ね近似しているが、2GHz付近にパッケージのLとCに起因すると思われるディップが発生する為、1GHzを超える周波数では、反射特性が乖離する。(5)ドライバー及びレシーバーモデルのポストシミュレーションによる解析波形比較

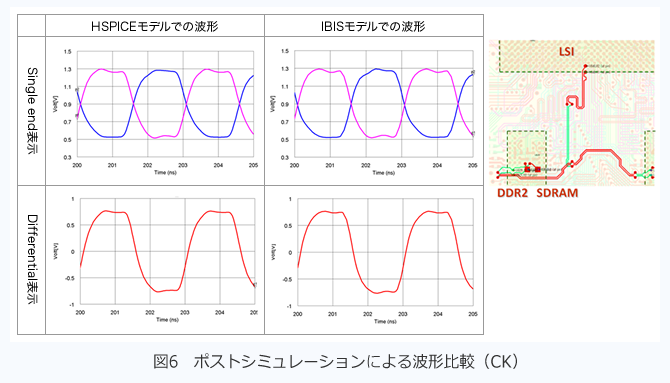

- CKは、LSIからの出力波形比較のみとなる。

- リンギングが発生しないシミュレーション系では、送出部のモデル差異による波形への影響は皆無であり、HSPICEとIBISの波形は、ほぼ同じと言える。(図6)

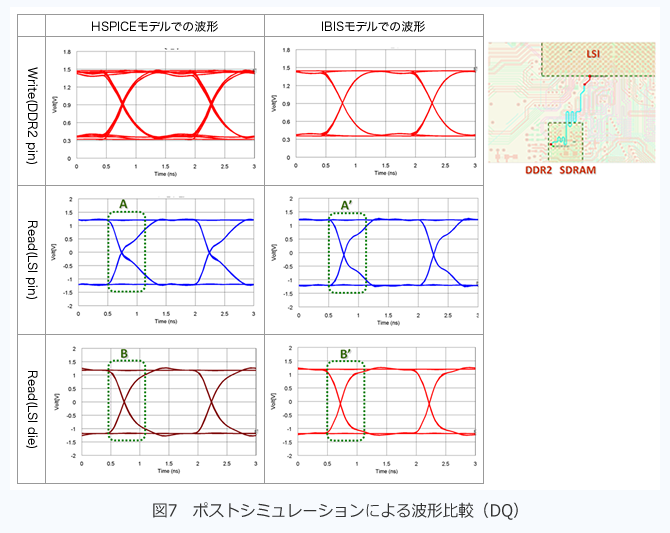

- DQ Write波形は、CK同様にLSIからの出力につき、目立った差異は確認されない。(図7)

- Read波形は、レシーバーの反射特性差異の影響により、

①PINでは、立ち上り(立ち下り)の段が付く位置に差が生じる(A点-A’点)

②Dieでは、立ち上り(立ち下り)の傾きに若干違いが生じる。(B点-B’点)

3.まとめ

高精度な波形解析やリンギングが強く発生する伝送路条件では、IBISはHSPICEにやや劣るが、トポロジー検討や妥当性確認では、使用に問題無いレベルである。

無料ダウンロード!

【ダウンロード資料例】

- DDR3メモリバスの設計手法

- 差動伝送路の設計と信号品質

- 12G-SDIリターンロス規格合致のための基板設計手法

- IBIS-AMIモデルを用いた高速信号シミュレーション

- 10Gbps超伝送の基板設計最適化

など全70テーマ

この機会に是非ご登録ください。 ※会員登録は無料です。