プリント基板総合メーカー|RITAエレクトロニクス株式会社 > 技術資料 > 高速シリアル伝送及び高速大容量メモリインタフェース パターン設計時の注意点まとめ

高速シリアル伝送及び高速大容量メモリインタフェース

パターン設計時の注意点まとめ

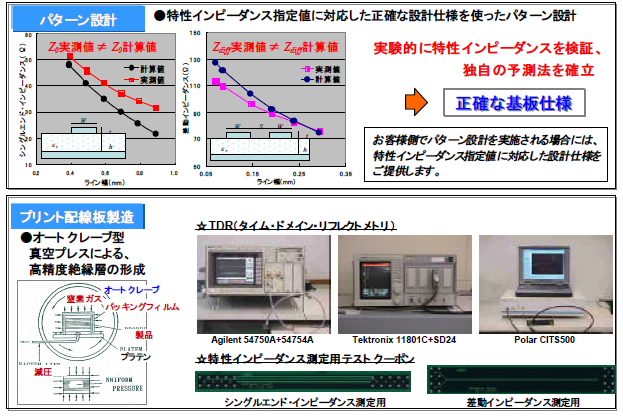

特性インピーダンスの計算式と実測値とのずれ

高速信号伝送の注意点として、よく配線の特性インピーダンス整合の必要性が言われます。

所望の特性インピーダンスを有する配線を実現する為に必要なものは

・特性インピーダンスの配線を実現する正確な層構成,配線仕様

・上記仕様を反映したバラツキの少ない基板製造

・最後に製品の実測

です。スライドのグラフはシングルエンド配線,差動配線のインピーダンス理論式の計算結果と実測値を示しています。グラフから計算結果は、実測値と一致しない事が判ります。実際のプリント配線板は製造ファクタを加味されて作られます。弊社では、あらゆる配線仕様のテストパターンを作成、実測し、その結果から独自の補正方法を導き実測値ベースでお客様に層構成,配線仕様を提示させて頂いています。(弊社にパターン設計をご依頼頂けば、弊社内で仕様の伝達を行い、お客様のお手を煩わす事なく所望のインピーダンスの配線を実現します)

また、弊社では製造において板厚精度の高いプレス機で基板をプレスする事で絶縁層厚の精度を高め、インピーダンスの誤差を少なくします。

製造された基板は、TDRという、反射波を使ってインピーダンス測定を実施する測定器を用い、製品外に設けたテストクーポンのインピーダンスを実測し保障致します。パターン設計の注意点として、基板メーカーから正確な配線仕様を入手することが重要です。

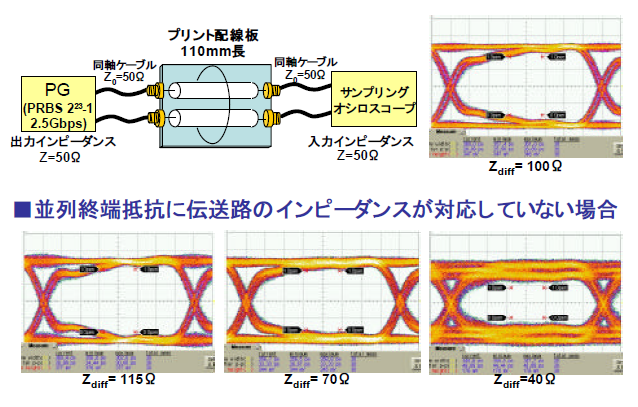

インピーダンス・ミスマッチが伝送波形に与える影響

基板配線のインピーダンスが設定からずれると、具体的にどのような影響があるか、実験例を紹介します。出力インピーダンスが50Ωの信号源を用い、2.5Gbpsのランダム信号を出力して、50Ω終端のオシロスコープで波形を観測する系で実験しました。この間の基板の特性インピーダンスを差動で100Ωという設定通りのほか、115Ωという高め、70、40という低めに変えてアイパターンを測定した結果です。

10%の変化ではそれほど影響はない結果ですが、30%や、それ以上ずれますと、しだいにアイが閉じてくることが分かります。

つまり、GHz級の信号伝送でも、やはり特性インピーダンスのコントロールが重要ということがお分かりいただけたと思います。

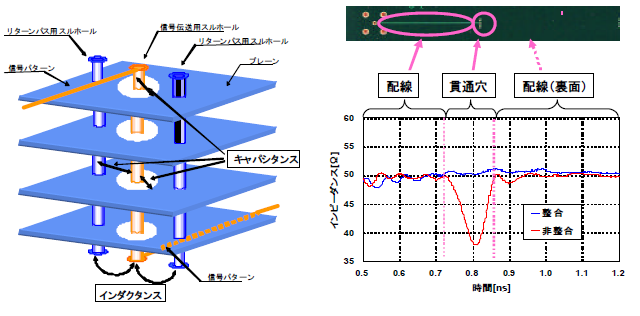

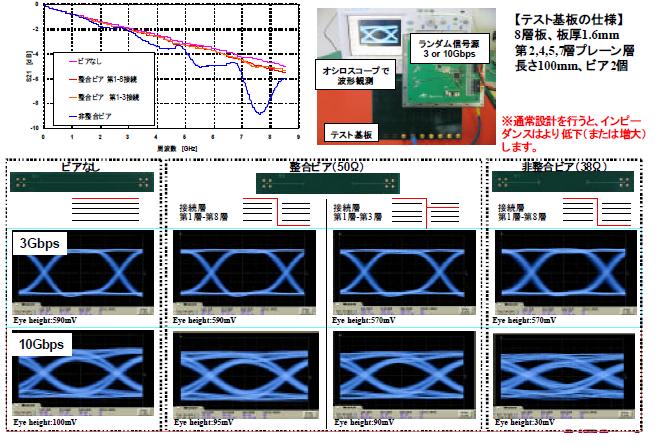

インピーダンス整合スルホール

ボード上の信号伝送速度が3Gbpsを超えだすと、局所的なインピーダンス不整合であっても信号品質を劣化させてしまう。配線密度が高まるにつれて基板の層数を増やし、スルホールを介して層間を接続する必要が生じてくる。この層間接続のスルホールはプレーンとのキャパシタンスやリターン経路によるインダクタンス、オープンスタブなどの影響により、インピーダンスが予測困難となり、信号経路とのインピーダンス不整合により、反射や共振が発生する。

基板上で信号が伝わる部分としては、配線だけでなく、部品実装用のパッドや、スルーホールなどがあります。このパッドは部品のリード形状や実装機に依存しますので、調整は難しいのですが、スルーホールについてはある程度細工ができます。GHz伝送では、配線だけでなく、スルーホールのインピーダンス・コントロールも重要な場合がありますので、その実例を紹介します。

左下図スルーホール近傍の断面的な斜視図です。配線に信号が流れますと、その近くの導体にリターン電流が流れること、その流れの経路を確保することが高速信号伝送では重要で、スルーホールについてもリターン電流経路の確保が重要とは良く言われることです。図で示すとこのようになります。

ここで、穴の径や間隔を適度にコントロールしますと、このスルーホールについてもTDR測定上の特性インピーダンスを配線とほぼ同じレベルにできます。

右下図はTDRで特性インピーダンスを測定した際の実測結果でして、横軸は時間で、縦軸は特性インピーダンスです。時間は、測定点からの距離に対応していまして、この凹むまでが配線で、凹んでいるところがスルーホール、これ以降が基板裏面の配線になります。スルーホールの仕様を調節することによって、そのインピーダンスを配線と同程度にできることが分かると思います。

整合ビアの伝送特性

ランダム信号の速度が3Gbpsの場合ですが、ビアがない場合、ある場合(整合ビア)、ある場合(非整合ビア)すべてアイが開いたアイパターンになっています。しかしよく見ると、インピーダンスコントロールできていないスルーホールを経由した場合に波形が若干汚い状況ですある事も確認できます。

10Gbpsになりますと、ビアのインピーダンスをコントロールすれば波形は良好で、10Gbps伝送が可能なことが分かりますが、ビアのインピーダンスが指定と異なる場合、アイはかなり潰れています。

Gbpsクラスの信号を基板に伝播させようとした場合、スルーホールのインピーダンス・コントロールが重要といえると思います。(10Gbpsでは必須)

インピーダンスをコントロールしたスルーホールはビアにオープンスタブがある場合でも整合は可能です。

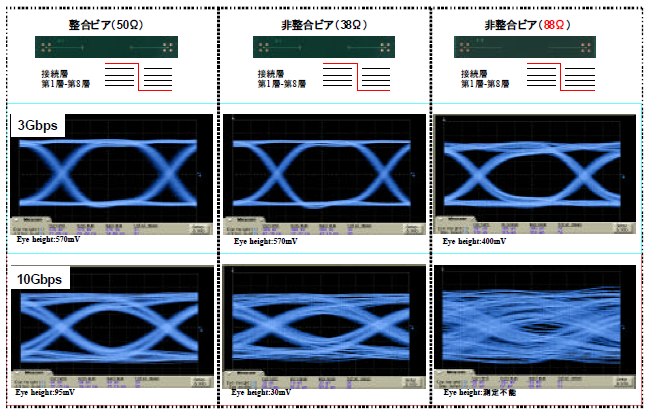

整合ビアの伝送特性(補足)

前スライドに補足してインピーダンスが高くなった場合の透過波形を記します。

10Gbpsではアイが完全に潰れてしまっています。

弊社では、理論に実記検証を加え、独自の手法でビアのインピーダンス整合を実施致します。実施には、条件が必要なので、メール等でお問い合わせ願います。

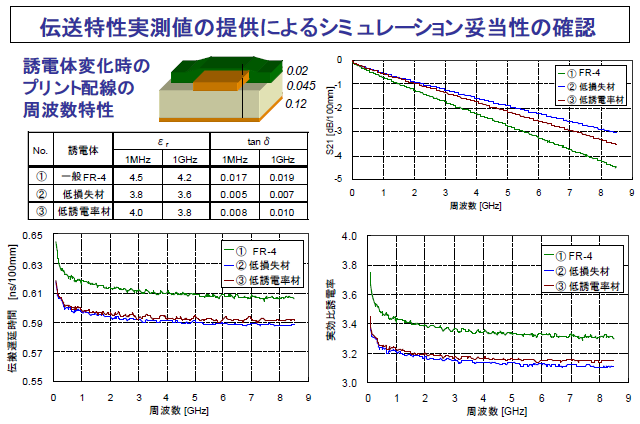

材料種別,厚みの違いよ伝送特性

さて、ここからは伝送損失についてご説明します。

伝送損失は、主に配線の導体損失と誘電体を介して漏れる誘電損失の和です。配線幅が変われば導体損失が変わりますし、誘電体である基板材料の条件が変わると誘電損失が変わります。基板材料には真空誘電率を1とし、その比で表した比誘電率(εr)と、ロス分の割合を示す誘電正接(tanδ)があり、材料の種類それぞれで値を持っています。このスライドでは、一般FR4,低誘電率材料,更に低損失材料の特性の実測値を比較しています。右上は配線の透過特性を示すS21です。縦軸は入力信号に対する透過信号の割合を対数で示しており下に行く程信号が損失している事になります。3種類の材料を見比べていただくと違いがある事がわかります。同じ材料でも、絶縁層(誘電体)厚が変われば、若干違った特性を示します。

これは、シミュレーションでも確認する事ができますが、シミュレーターに与える材料の特性値(誘電率,誘電正接)が材料のカタログ値で良いのか疑問です。弊社では、基板材料の違い,絶縁層厚の違い,配線仕様の違い,レジスト色の違い等を変化させ、それぞれの場合の単位長さあたりの特性を実測値からデータ化しています。

お客様から、お問い合わせ頂ければ、それら実測結果をご提示し、材料選定の検討、配線仕様の検討にお役立て頂ける準備がございます。

特性インピーダンス同様、伝送損失量の想定も実測値をベースとする事がベストであると考えます。

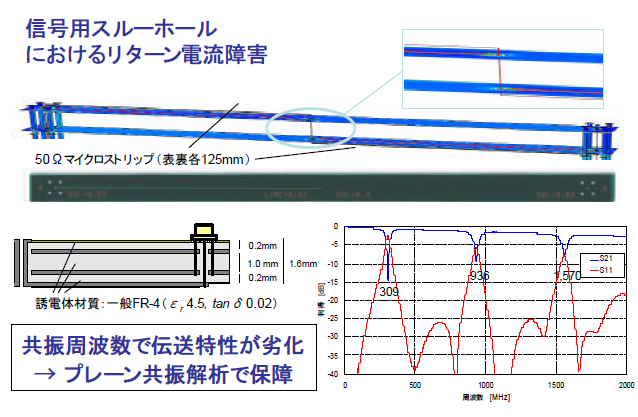

リターンパス不連続(電源/GNDプレーン設計)

次に、基板設計でいえば、電源やグラウンドのプレーンの設計がしっかりしていないと、信号波形に思わぬ悪影響を及ぼすことがあります。

前のスライドで、インピーダンスをコントロールしたスルーホールのお話をいたしましたが、その場合はリターン電流の経路が近傍にあるという理想的な設計でした。しかし、メモリバスなど、現実的にはこの斜視図のように、単純にスルーホールがべたプレーンを貫通している部分が多いのが実態と思います。

右下のグラフは、スルーホールを含む配線について、ネットワークアナライザーで伝送特性を測定した結果です。縦軸は利得で、横軸はGHzまでの周波数、青が透過で下ほど減衰、赤が反射で上ほど反射大でよろしくないことを表しています。

特定の周波数で信号がほとんど透過せず、信号伝送に悪影響があることを表しています。

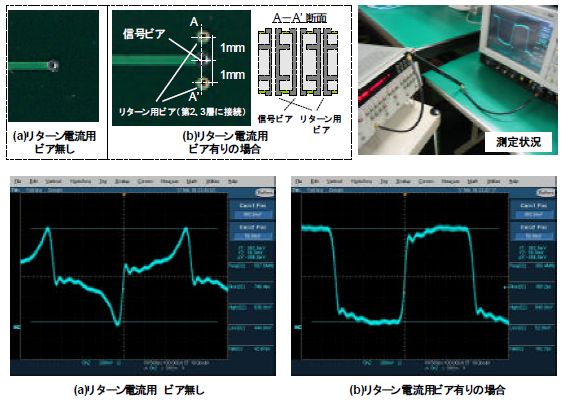

300MHz矩形波の基板経由後波形

前スライドのグラフで、信号が透過できない約300MHz付近のクロック信号を、配線の入力しその時の波形を測定したのが左下の波形です。

S21で表したように、伝送波形も基本となる周波数が伝送できず、歪んだ波形となっています。これに対し、信号ビア近傍にリターンパス用のビアを配置すれば、右下の波形のようにきれいなパルスが透過できます。

実際の基板では、電源/GND層がもっと大きく、コンデンサとしてリターンパスを確保していたり、近傍のデバイスにGNDビアやバイパスコンデンサが配置され、それらをリターンパスとする事で現象があまり顕在化していないと思われます。

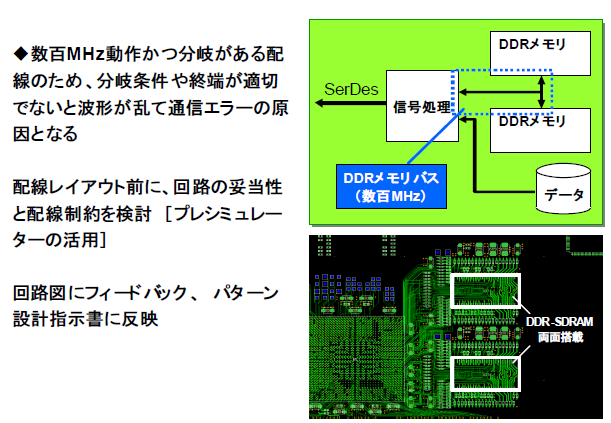

高速メモリ(DDR)バス設計

数GHz級の高速信号伝送は通常1対1のため、分岐がある場合の反射などの影響はほぼ考慮する必要がありませんので、特性インピーダンス,伝送損失,リターンパスを考慮していればうまくいきます。しかし、メモリバスの場合は1対多で分岐があり、しかも周波数があがっていますので、分岐や終端処理の条件がしっかりしていないと波形が汚くなり、通信エラーにつながることが多い実態があります。

これを解決する手段としては、まずは高速メモリバス系のパターン設計ノウハウが大前提として必要で、さらにシミュレーターと使ってパターン設計前の段階で短期間に波形を確認して、分岐長や終端方法の許容範囲を見出し、抵抗の追加が必要や、または削除できる場合は、お客様の回路図に反映するとともに、パターン設計指示書を作成して、これに基づいた設計が必要ということになります。

プレシミュレーションによる配線トポロジーの抽出①

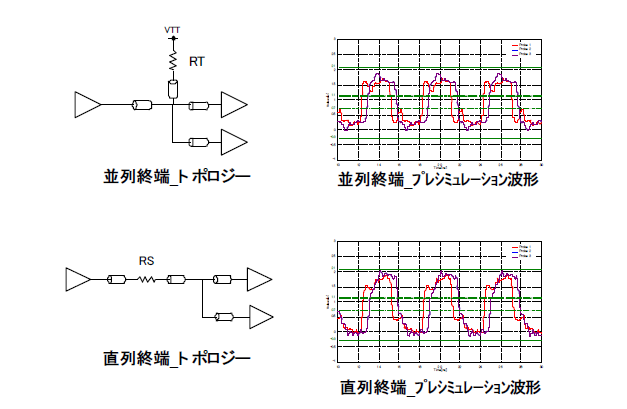

ここでは、分岐配線(アドレス)に対する終端条件の確認を行っています。

直列終端のみ,並列終端のみ,直列並列終端の併用,終端抵抗を搭載しない、といった選択肢があるかと思います。これらは、それぞれ違った波形を示します。

回路図検討の段階で、まずどの終端が適切であるかを見極める必要があります。

バス配線は部品実装密度,配線密度が高い状況でのパターン設計となります。

部品点数を抑えたい,消費電力を少なくしたいといった波形品質以外の要求事項もある事でしょう。この段階でのシミュレーションでは、このような要求を加味した上で波形品質として納得できる妥協点を見出す事ができ、回路図面にフィードバックされます。ここでポイントとなるのが、配線の長さです。DDR等の高速メモリーインタフェースの場合は配線も部品の一つと考える事が必要です。

分岐数,終端条件を加味した、現実的な配線長でのシミュレーションを実施し、終端条件等を判断する必要があります。

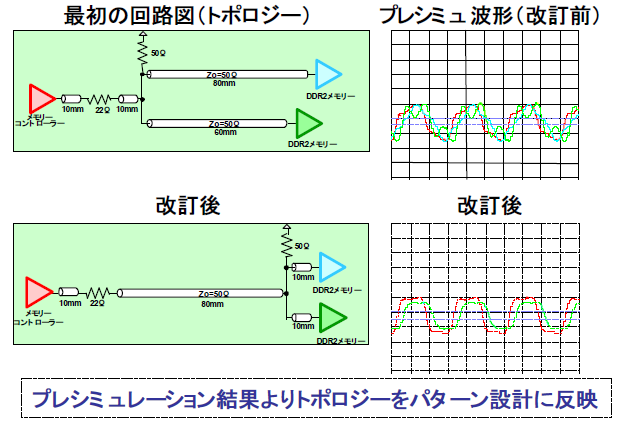

プレシミュレーションによる配線トポロジーの抽出②

このスライドの回路は回路図としては、2分岐の配線で、直列終端,並列終端を併用しており、まったく同一です。しかし、分岐のポイント、分岐後の長さを変えると波形は大きく変化します。右にシミュレーション波形を記していますが、改定前ひどく乱れていた波形が改定後はキレイな波形となっています。

パターン設計を開始する前に、このような条件をシミュレーションによって抽出し、これら、分岐や配線長の条件の許容点を、パターン設計条件書に記載する事で、パターン設計の精度を高める事が可能です。

パターン設計を実施する上で、これら条件の許容点を明確にし、設計から基板製造に移行する事でリスクを回避する事ができます。

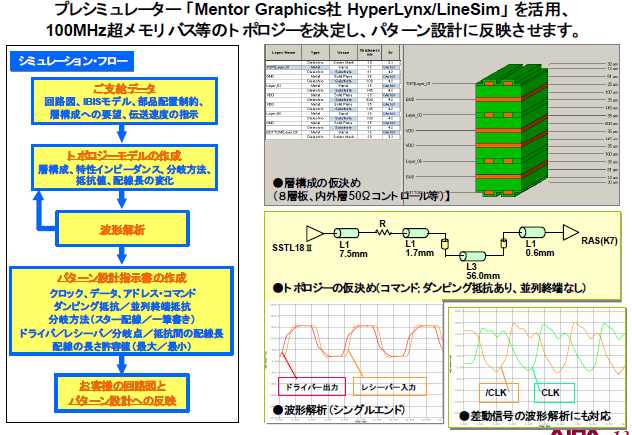

プレシミュレーターを活用したトポロジー決定サービス

アイカ工業では、前の2スライドのようなプレシミュレーションをお客様のパターン設計案件に実施させて頂いています。

回路図をお預かりし、終端抵抗の条件を変更してシミュレーションを実施し、推奨回路を提案させて頂きます。

また、終端抵抗の配置位置、分岐ポイントまでの配線長,分岐後の配線長の許容点を波形シミュレーションより求め、これをお客様にご納得頂いた上でパターン設計条件書の追加版として発行し、パターン設計の精度を高めます。

使用するデバイス(メモリーコントローラー,DDRメモリー)によっても始端部,終端部のインピーダンスやドライブ力に差異があり、また信号の速度,立上り、立下り時間によっても波形に大きな違いが現れます。

DDR搭載基板のパターン設計において重要なポイントは、CLK,ADR/CMD,DQ/DQS等それぞれの配線に応じていかに最適なトポロジーを選択するかです。アイカ工業では、プリシミュレーションとコンサルティングによりお客様により最適なトポロジーの提案を行います。

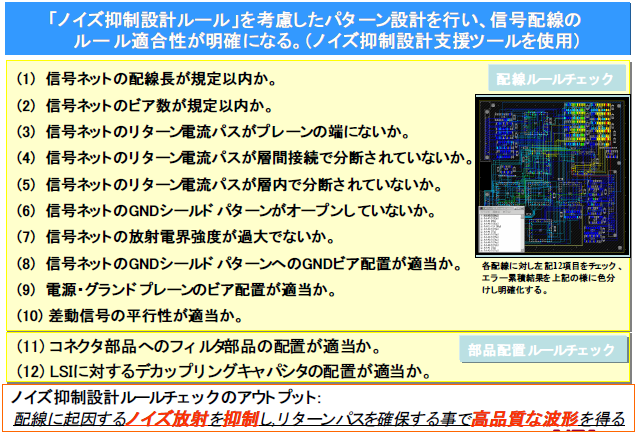

ノイズ抑制設計ルールチェック

このスライドでは、ノイズ抑制設計についての弊社の取り組みをご紹介します。

弊社では、ノイズ抑制設計支援ツールを用いた設計を推進しています。

プリント配線板はアンテナの要素が複数存在しています。パターン設計中の配線が放射し難いものになっているか否かを12項目についてチェックを行い、エラーポイントを累積し、配線毎に表示します。この結果を元に部品配置や配線を変更し放射の少ないパターン設計を実現致します。

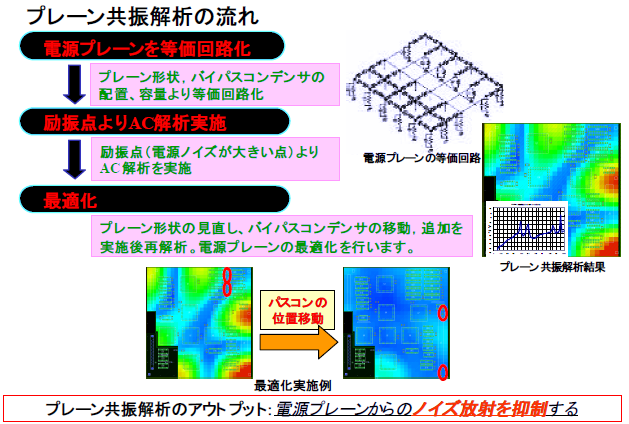

プレーン共振解析(ノイズ抑制設計)

また、電源プレーンについては、プレーン共振解析を実施し、バイパスコンデンサの追加,移動、プレーン形状の見直しを行う事で、プレーンからの放射の少ない設計を実施しています。

DDR等の高速バス配線は、電源に対する負荷も大きくなります。ノイズが出難い設計が求められます。

無料ダウンロード!

【ダウンロード資料例】

- DDR3メモリバスの設計手法

- 差動伝送路の設計と信号品質

- 12G-SDIリターンロス規格合致のための基板設計手法

- IBIS-AMIモデルを用いた高速信号シミュレーション

- 10Gbps超伝送の基板設計最適化

など全70テーマ

この機会に是非ご登録ください。 ※会員登録は無料です。

関連情報

- プリント配線板における高速シリアル伝送の注意点

- 高速信号伝送におけるビアの影響

- コネクタやケーブルの実測ベース電気モデル

- SMA レセプタクルの信号線径・穴径とSパラメーター

- フローティング層が高速信号伝送に及ぼす影響

- プリント配線の発熱シミュレーションの高精度化に関する検討

- プリント配線の曲げが伝送特性に及ぼす影響

- 高速差動信号伝送におけるプリント配線板リファレンス面の影響

- 部品実装部位の特性インピーダンスコントロール手法の検討

- 差動配線のスリットまたぎに起因するノイズ

- リジッドプリント配線板

- プリント配線板における高速大容量メモリ(DDR)インタフェースの注意点

- 高速シリアル伝送及び高速大容量メモリインタフェース

パターン設計時の注意点まとめ