プリント基板総合メーカー|RITAエレクトロニクス株式会社 > 技術資料 > プリント配線板における高速大容量メモリ(DDR)インタフェースの注意点

プリント配線板における高速大容量メモリ(DDR)インタフェースの注意点

はじめに

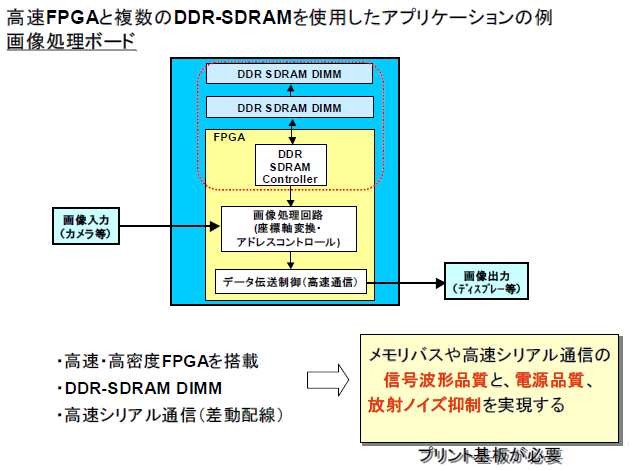

まずはじめに、スライドのような画像処理ボードを例に、高速FPGAと複数のDDR-SDRAMを使用した基板の説明を行います。

このボードの特徴は

1.高速・高密度なFPGAが搭載している。

2.DDR・SDRAM(DIMM)が複数搭載している。

3.高速シリアル通信ラインがある。

です。高速・大容量メモリーを用いて処理を行う基板には、基板外と大容量のデータ伝送を実施するケースが多いと考えられます。

このような基板に要求させる事は

●信号波形品質

●電源品質

●放射ノイズ抑制

となります。

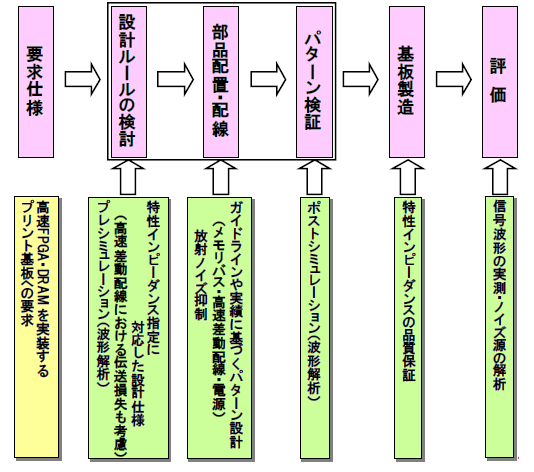

プリント基板開発の流れ

次に、この様な高速・大容量メモリーを搭載したプリント配線板開発の流れを説明します。

まず、はじめに、当然のことですがプリント基板を作るにあたり、設計した回路をどのぐらいの大きさの基板に納めるとか、基板層数を何層するとか、パターンの特性インピーダンスをどのようにするとかといった具合に、基板に対する要求仕様があります。

つぎに、要求仕様に則った設計仕様の検討があります。

DDRインターフェースや高速差動配線には特性インピーダンスの整合が求められます。

従って、基板層数,基板厚等を元に層構成を決定し、特性インピーダンスに合った配線幅,配線間隙を検討します。(これには基板メーカーからの正確な情報が必要です)

また、この段階でプレシミュレーションを実施する事で配線それぞれのトポロジーを決定し、パターン設計時の制約条件とします。

パターン設計は、JEDEC,各メモリーメーカーが公開しているデザインガイドや、過去の実績、そしてプレシミュレーションより決定したトポロジーを反映させます。

設計が完了するとその設計の妥当性を確認する為にポストシミュレーションを実施します。(設計の妥当性確認。基板製造を実施する最終確認)

基板を製造し、テストクーポンで特性インピーダンスの実測(保障)を行った後、部品実装、評価へと進みます。

基礎知識(1)

それでは、基礎知識の部分から見ていきます。

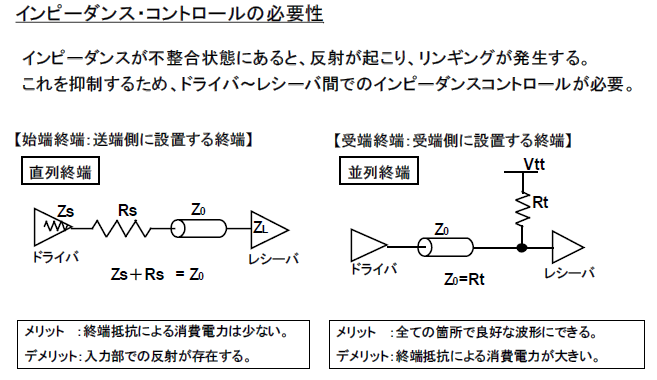

まず、インピーダンス・コントロールの必要性についてですが、ここでは、インピーダンスの不整合によってどのようなことが起こり、またその時、どのようにすればよいのかについて簡単に紹介します。

まず、インピーダンス不整合の状態にありますと、素子の駆動能力にもよりますが、信号の反射と言う問題が起こり、オーバーシュートやアンダーシュートを招き、リンギングなどの問題が発生します。対策として、配線のインピーダンスを層構成及び配線の仕様検討、基板製造の段階からコントロールし、またドライバ、レシーバの素子間に抵抗などを挿入してマッチングさせます。

直列終端はドライバー側に抵抗を直列に配置し、レシーバーで反射した信号をドライバー部で完全に消費させ、ドライバー部での再反射を抑制する方法です。

並列終端は、レシーバーに対し並列に抵抗を配置し、ドライバーから出力した信号をレシーバー側の抵抗で全て消費させ、反射を発生させない方法です。

(抵抗は、GNDや終端基準電位に接続します)抵抗値は、スライドに記載したように配線の特性インピーダンス(Zo),ドライバー部出力インピーダンス(Zs)により最適値を求めます。

基礎知識(2)

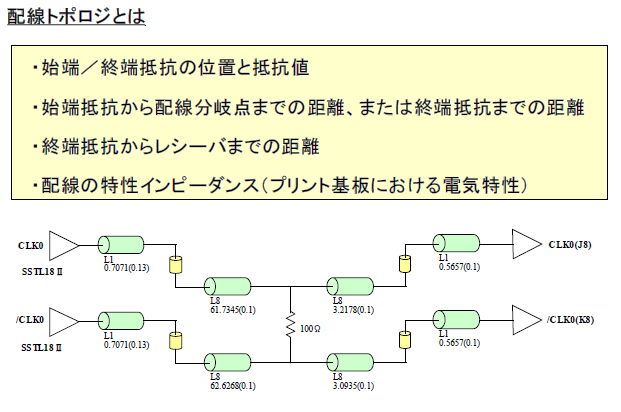

配線の引き回し等の仕様を配線トポロジといいます。

具体的には、

①直列終端抵抗、並列終端抵抗の位置や抵抗値

②直列終端抵抗から配線分岐点までの距離、または並列終端抵抗までの距離

③並列終端抵抗からレシーバまでの距離

④配線の特性インピーダンス

等がこれに当たります。回路図が同じでも、分岐方法を変えるだけで波形は大きく変化します。

最適なトポロジーを得る方法としてプレシュミレーションが活用する方法がありますが、これは後のスライドで説明します。

基礎知識(3)

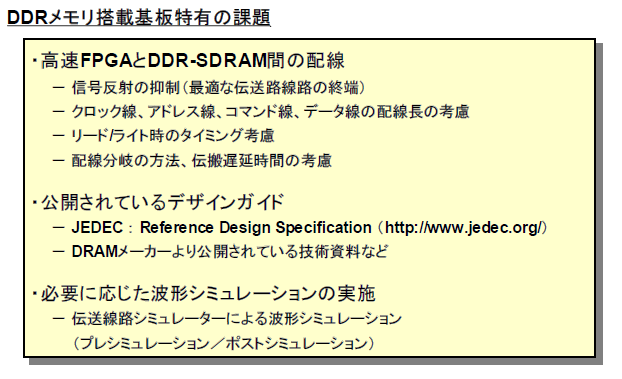

さて、DDRメモリーを搭載する基板には、特有の課題があります。

これらをスライドに表しました。

反射抑制やタイミングへの考慮を実施し、また公開されているデザインガイドを参照して課題解決に努めなければなりません。

前スライドに引き続き、シミュレーションでの確認が非常に重要になる事を書き加えておきます。

設計仕様の決定(1)

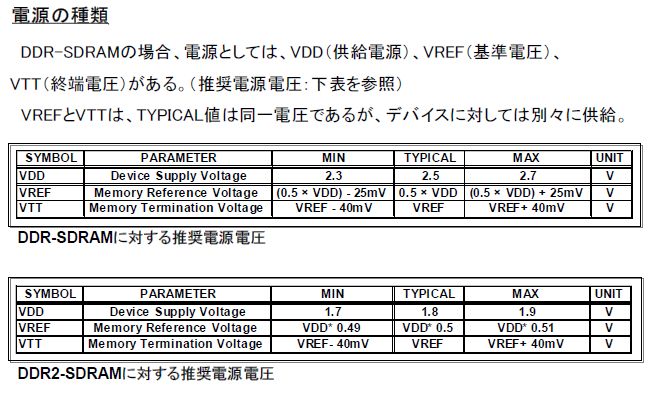

電源の種類も多彩です。

終端用電源と信号の基準電源の電位は同じなのですが、使われ方の違いよりその設計方法も差異があります。

メモリーコントローラーにFPGAを使用する場合、更に多種の電源が必要となりAW設計の難しさが増加します。

設計仕様の決定(2)

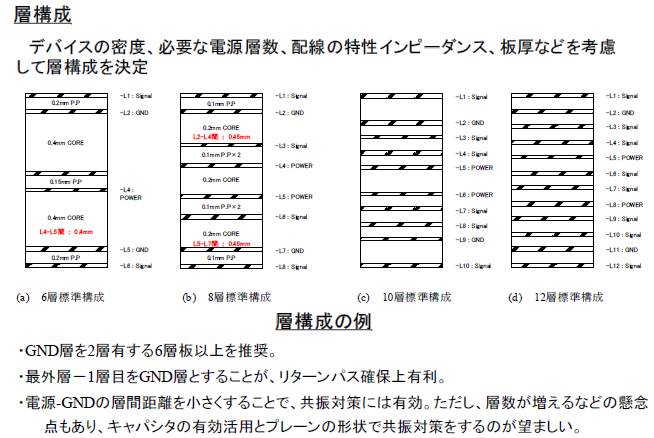

次に層構成案です。

スライドには6層,8層,10層,12層の例を示しました。

最外層(10層板の場合L1,L10)から-1層目(10層板の場合L2,L9)をGND層とする事で信号線に対するリターンパス確保に有利となります。

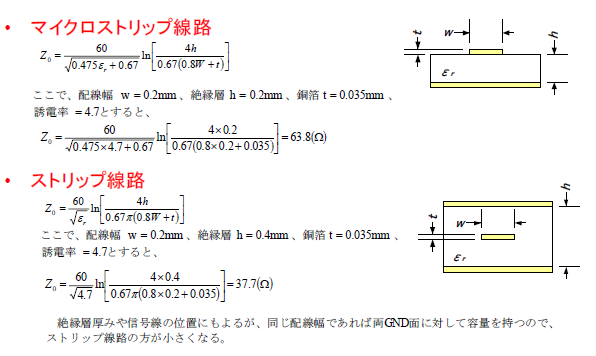

配線の特性インピーダンス

配線の特性インピーダンスは、マイクロストリップ線路,ストリップ線路ともスライドのような計算式(理論式)で求められます。

ここで、仮に配線幅(w=0.2mm)、絶縁層厚(h=0.2mm)、銅箔厚(t=0.035mm)、比誘電率(εr=4.7)を与え、配線の特性インピーダンスを計算すると、マイクロストリップでは、63.8Ω、ストリップでは37.7Ωとなります。同じ配線幅であれば、ストリップ線路の方がインピーダンスが低くなります。

これは、ストリップ線路が上下のリファレンス層(GND層)に対して容量成分を持つからです。

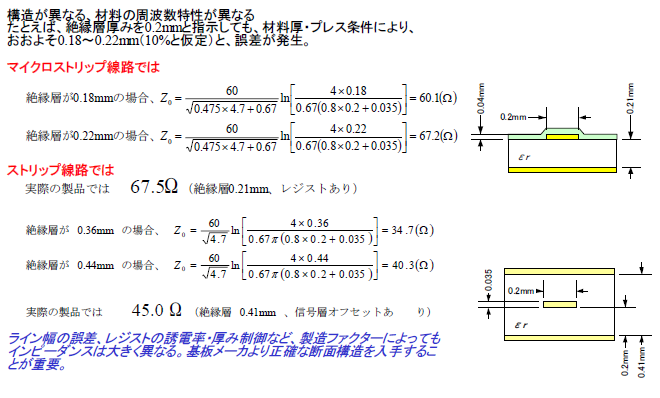

配線の特性インピーダンス(実際)

実際に製造上のばらつきが発生した場合、配線の特性インピーダンスにどのくらい影響を与えるかを計算してみます。

マイクロストリップ線路で絶縁層が-10%の0.18mmになるとインピーダンスは60.1Ω、+10%の0.22mmになると67.2Ωという計算結果になります。

ストリップ線路でも同じ事が言え、34.7Ωと40.3Ωという計算結果になります。

実際のプリント配線板では、レジストがあったり絶縁層が違ったりし、また、計算式(理論式)の精度にも影響を受けます。マイクロストリップ線路で配線幅等の仕様がもっとも近い基板の配線の特性インピーダンスを実測すると67.5Ω程度となりました。

同じくストリップライン線路では弊社の実績のある近い仕様では、約45Ωという結果を得ています。

計算式(理論式)から得た配線の特性インピーダンスと実際に作成した基板の配線の特性インピーダンスは、必ずしも一致しません。

弊社は自社の製品に配線の特性インピーダンスの保証を実施していますが、どのようにして高精度にインピーダンスコントロールを実施しているかは、次号でお知らせ致します。

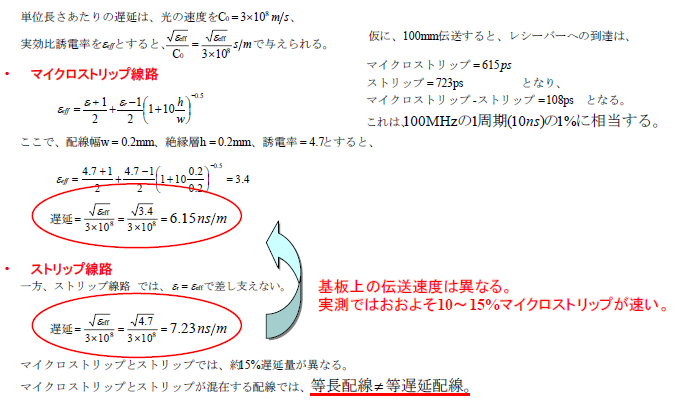

伝搬遅延時間について

次に、伝播遅延時間についてです。光の速度は1秒間に地球を7.5周します。これは30万km/secという速度になります。電気も真空中(空気中でもほぼ同じ)であれば光と同じ速度です。

ではプリント配線ではどうなるでしょう。

一般的なプリント配線板の材料は誘電体であり、電気信号の伝わる速度は光速を比誘電率の平方根で割った商に当たります。ここでご注意頂きたいのが、プリント配線板の外層を配線したマイクロストリップ線路とストリップ線路で伝播速度に違いがあるという事です。

ストリップ線路は、配線の周り全てが誘電体であり、実効比誘電率が基板材料の持つ比誘電率とほぼ等しいと言えます。

一方マイクロストリップ線路は、下半分が基板材料、上半分はレジストと空気という構造で実効比誘電率は簡易的にスライドに記載の計算式で求められます。仮に基板材料の比誘電率を4.7とすると、マイクロストリップ線路の実効比誘電率は3.4となります。

これら比誘電率を伝播遅延(1/速度)の計算式に代入すると、マイクロストリップ線路は6.15nsec/m、ストリップ線路は7.23nsec/mと求まり、その差は約15%程度となります。いくら高精度な等長配線を実施しても配線層が違えばスキューが発生してしまいます。

等長配線の真の目的が等遅延配線であるならば、メモリーバスのグループ分けを実施し、それぞれのグループで同一配線層とするといった制約を設ける必要があります。

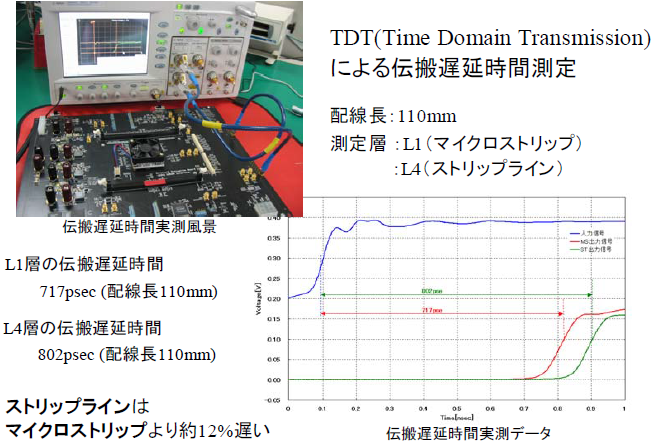

伝搬遅延時間の実測

では、先程の伝播遅延時間差を実測してみましょう。

測定対象となる配線は、両端にSMAケーブル実装できる110mmのテストクーポンです。L1(マイクロストリップ線路)とL4(ストリップ線路)にそれぞれ配線しています。測定にはTDT(Time Domain Transmission)という測定器を用います。TDTは反射を利用して線路インピーダンスを測定するTDRのオプション機能で、配線の片端から入力した急峻な立ち上がりエッジのステップパルスの透過時間をもう一方の出力波形を観測する事で得る方法です。

測定結果は、

マイクロストリップ線路では717psec/110mm (652psec/100mm)

ストリップ線路では802psec/110mm (745psec/100mm)

となりました。これは、ストリップ線路はマイクロストリップ線路より約12%遅いというものです。

実測結果からも、計算結果と同じく配線層が違えば速度(または伝播遅延時間)に違いが発生する事が確認できました。

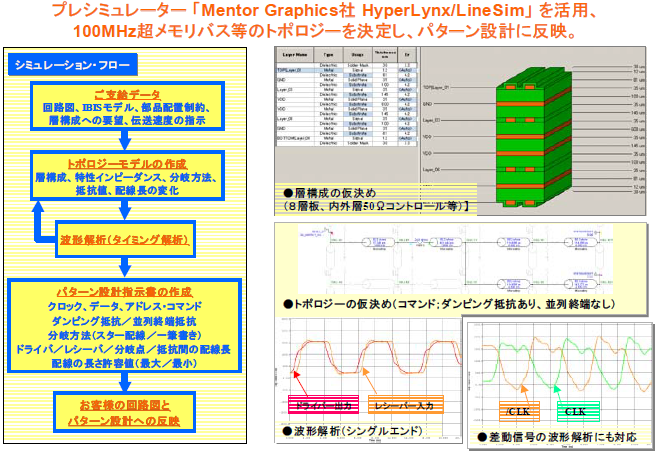

プレシミュレーターを活用したトポロジー決定

今までのスライドでは基礎知識にあたる部分をご説明しました。

ここからは、実設計に反映する内容をご説明致します。

先のスライドでもご紹介してますように、DDRのような高速メモリーバス設計の品質には、配線トポロジーが大きく影響します。ここではプレシミュレーションについてご案内します。プレシミュレーションの目的は、終端抵抗を追加・削除等を変更するといった回路図の確認及び変更とパターン設計を実施する為の制約条件を導き出す事です。

前回ご案内した高速シリアル伝送は、インピーダンスミスマッチの排除と伝送損失への考慮がポイントですが、メモリーコントローラーとDDRメモリー間の配線には、分岐が存在する,双方向伝送である,配線が密集する事で最適場所に終端抵抗を配置する事ができないといった、インピーダンスミスマッチの要素が、回路図の段階や物理的な制約から既に内在しています。高速シリアル伝送はベストを目指しての設計なのに対し、DDR基板設計は、インピーダンスミスマッチがあっても波形品質として許容できる設計を行う事になります。

上記を得る為に、プレシミュレーションを実施し、トポロジーを抽出しておく事が重要となります。

パターン設計を開始する前に上記の許容点を明確にしパターン設計時の条件とする事で、後戻りの少ない商品開発を実現します。

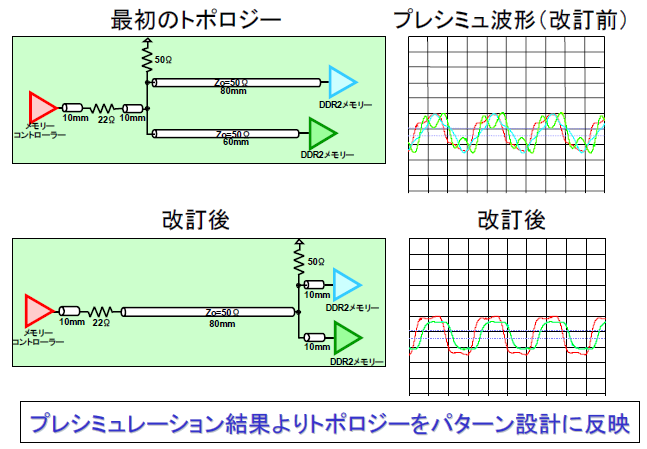

プレシミュレーション実例

プレシミュレーション例を試します。

上記2種類のトポロジーは、回路図としては同じです。しかし、分岐までの長さ、分岐後の長さ、並列終端抵抗の配置の違いにより、波形品質に大きく影響を与えるのです。

改定後のトポロジーでも、メモリーコントローラからの出力信号がさらに急峻になれば、分岐が2本のスタブとして振る舞い、波形を乱すかもしれません。しかし、今回のシミュレーションではメモリーコントローラーの出力(ドライブ力),直列終端抵抗,並列終端抵抗の位置、分岐後の配線長と条件より、十分にキレイな波形を得る事ができています。

このようにして、配線長、分岐長、抵抗の配置の条件を導き出し、パターン設計の条件とするのです。

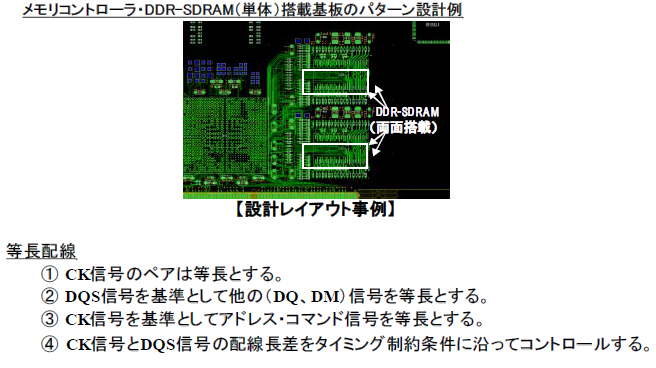

等長配線

パターン設計の制約条件として等長配線指定があります。

この指定も最適に実施して頂く必要があります。

回路設計者は、「完全等長」と指示される場合がありますが、過剰な等長配線指示は、

・配線長が長くなる。

・等長配線作業で設計納期に影響が出る

・場合によってはクロストークに影響で誤動作

といった悪影響を及ぼす可能性もあります。等長配線の指示は、アドレス・コマンド系、CK、DQS・DQといったそれぞれの種別毎に、またDQSとDQといったグループ毎にそれぞれの性格に従った等長配線指針を指示する必要があります。

CKの差動ペア配線の等長配線とDQSを基準にしたDQの等長配線では、目的も許容値も違います。

完全等長配線が必ずしもベストな配線では無いことをご認識ください。

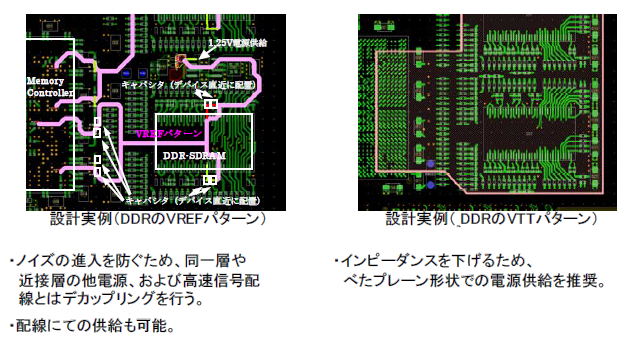

電源配置

DDR搭載基板では、アドレス・データといった配線以外にも電源系の配置に注意する必要があります。

先のスライドでもご説明しましたが、VrefとVttは同電位ですが、別配線での供給となります。

Vrefは信号ラインの基準電位として与えるもので、大きな電流が流れる事はありません。従って、わざわざ1層を用いて電源供給する必要はなく、太い配線を用いて供給する事も可能です。

ただし、基準電位なので、電圧の安定性が求められます。他の電源や配線からの影響を受けないように配置する、デバイス近傍にはコンデンサを配置し、更に安定させるといった注意が必要です。

対して、Vttは信号終端に用いる電源です。信号線が変化する度に、過度的に電流量が変動します。DDRは多ビットのバスラインを使用するので、前記信号変化が複数の同時動作となる為、これに対応した電源配置が必要となります。

電源のインピーダンスを下げる為、VttはVrefとは異なり、ベタプレーンでの供給が必要となります。

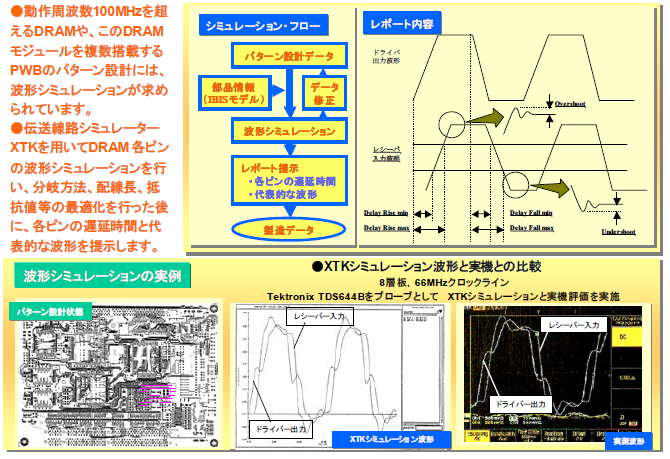

伝送線路シミュレーション技術(ポストシミュレーション)

パターン設計が完了すると、その設計データで基板製造作業に進めて良いかの最終ジャッジをする為、パターンデータを用いたポストシミュレーションを実施し、波形を確認しておく事もお勧めです。

プレシミュレーション同様にシミュレーション波形による確認となりますが、プレシミュレーションは、パターン設計の精度を高める為に実施する、ポストシミュレーションは、出来上がったパターン設計データで基板製造を実施するかの判定の為に実施する、といった具合にその目的が違います。

これらシミュレーションを効率よく活用し、与えられた開発スケジュールで安定した動作を行う基板の製造へと進めていきます。

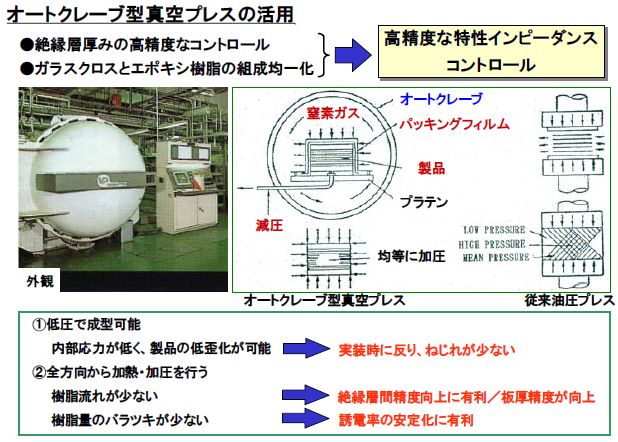

基板製造(1)

パターン設計が完了すると、次は基板製造です。

高速信号を高品質に効率よく伝送するには、インピーダンスマッチングが求められます。要求した特性インピーダンスのプリント配線を得る為には、

①高精度な基板仕様の検討

②上記仕様を実現する為の製造

の2点が必要です。スライド9のインピーダンス計算式の変数として、パターン幅(w),絶縁層厚(h),パターン高さ(t),基板材料に比誘電率(εr)があります。

ここでは、絶縁層厚を高精度にコントロールする為の弊社の設備のご紹介をさせて頂きます。

スライドの設備はプリント配線板を積層するプレス機です。

弊社のプレス機は、オートクレーブ型真空プレスといって、積層する基板をパッキングし、そこから真空ポンプで減圧するとともに、周りに窒素ガスを注入する事で全ての方向から、圧力を加える事ができ、従来の油圧プレスを用いるより、高精度な絶縁層厚を得ることが可能です。

結果、高精度な特性インピーダンスコントロールが実現します。

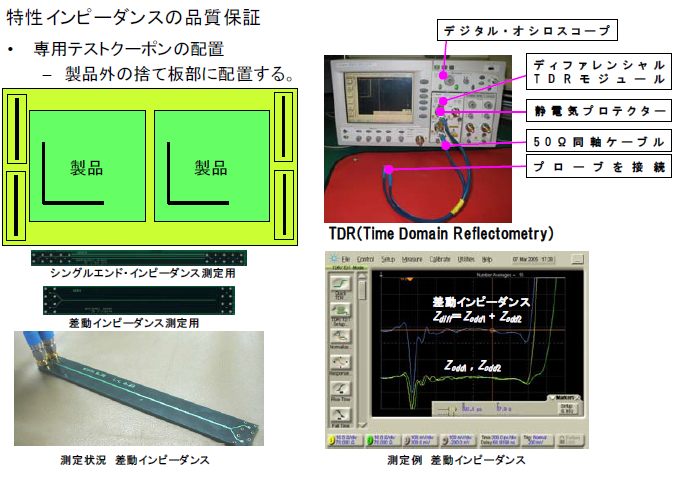

基板製造(2)

最後に品質保証です。

特性インピーダンスコントロールを要求したプリント配線板は、要求仕様通りに基板が出来上がってきたか、確認が必要です。

これは、製品上に配置された配線と同一仕様のテストクーポンを製品外に配置し、これをTDR(Time Domain Reflectometry)で実測する事で保証致します。

弊社では、通常±10%の範囲でテストクーポンの特性インピーダンスを実測保証し、出荷致します。特性インピーダンス50Ωの場合、45Ω~55Ωが保証範囲となります。

特性インピーダンスの誤差が波形に与える影響は、次回お知らせする予定です。

無料ダウンロード!

【ダウンロード資料例】

- DDR3メモリバスの設計手法

- 差動伝送路の設計と信号品質

- 12G-SDIリターンロス規格合致のための基板設計手法

- IBIS-AMIモデルを用いた高速信号シミュレーション

- 10Gbps超伝送の基板設計最適化

など全70テーマ

この機会に是非ご登録ください。 ※会員登録は無料です。

関連情報

- プリント配線板における高速シリアル伝送の注意点

- 高速信号伝送におけるビアの影響

- コネクタやケーブルの実測ベース電気モデル

- SMA レセプタクルの信号線径・穴径とSパラメーター

- フローティング層が高速信号伝送に及ぼす影響

- プリント配線の発熱シミュレーションの高精度化に関する検討

- プリント配線の曲げが伝送特性に及ぼす影響

- 高速差動信号伝送におけるプリント配線板リファレンス面の影響

- 部品実装部位の特性インピーダンスコントロール手法の検討

- 差動配線のスリットまたぎに起因するノイズ

- リジッドプリント配線板

- プリント配線板における高速大容量メモリ(DDR)インタフェースの注意点

- 高速シリアル伝送及び高速大容量メモリインタフェース

パターン設計時の注意点まとめ