プリント基板総合メーカー|RITAエレクトロニクス株式会社 > 事例紹介 > 基板内差動配線のスルーホールとスリット跨ぎによる信号伝送劣化対策

基板内差動配線のスルーホールとスリット跨ぎによる信号伝送劣化対策

課題

差動配線のスリット跨ぎとスルーホール

プリント配線板内の差動信号配線には、層数等様々な制約によりリファレンスプレーンに生じたスリットを跨ぐことが避けられない場合やスルーホールを通過する等、信号伝送を阻害する要因が生じる場合があります。それら阻害要因の影響を低減する方法を説明します。

当社のご提案

- 1.差動配線のスリット跨ぎ

-

差動配線が内層ベタパターンのスリットを跨いだ場合の影響を実験で確認します。

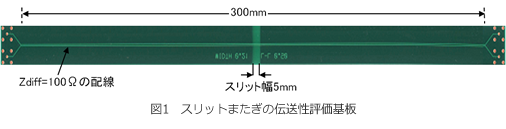

実験に用いる基板を図1に示します。

基板の特徴は、差動インピーダンス100Ωの配線が5mmのスリット幅を跨いだ場合の伝送特性への影響を確認するもので、差動配線はペア間の結合が”強い配線”、”中ぐらいの配線”、”弱い配線”の3種類を準備しました。

- 2.実験結果

-

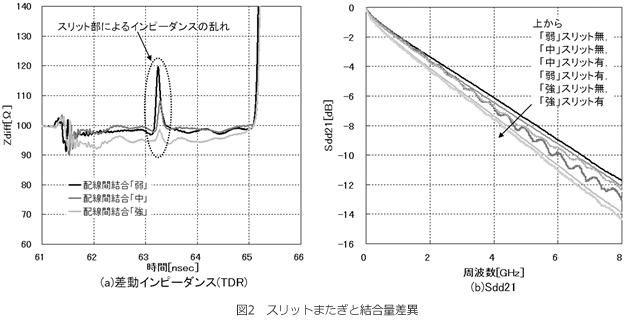

図2(a)にTDR(time domain reflectometry)法を用いた各基板の特性インピーダンスを示します。

63.2nsec付近がスリットによる影響によるもので、ペア間結合が強い程インピーダンスの乱れが生じ難く、結合が弱い程乱れが生じ易い事が確認できました。

また、図2(b)に伝送特性Sdd21を示します。

この測定結果から,結合が強いほどスリット有無によるSdd21の差が少ない事が判ります。

これは、結合が弱い配線では信号配線に対するリターン電流のほとんどがグラウンドや電源といったべたプレーンを流れるため、スリットによるリターン電流経路の不連続が生じるのに対して、結合が強い配線ではリターン電流の多くは互いのペア配線にも流れておりリターン電流経路は常に確保されています。

- 3.差動配線のスルーホール

-

他に,高速信号伝送の阻害要因としてスルーホールがあります。

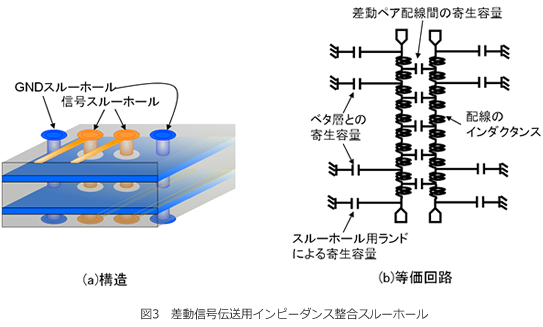

スルーホールは表層のランドやべた層通過部分では容量性を示し、樹脂部通過の部分は主に誘導性を示す為、それら容量性と誘導性のバランスによってスルーホール領域を配線の特性インピーダンスと整合することが可能です(図3)。

差動配線ビアの間隔、グラウンドビアとの間隔、ビア径およびべた通過部のクリアランス径が誘導性および容量性のパラメータとなるため、これらを適切に定める必要があります。

表層~裏層間の接続ではなく、内層に接続する場合は、電流が流れない部分がビアスタブとなり、インピーダンスの低下を招てしまいます。

容量成分が大きい場合は、その容量成分に応じて誘導成分を大きくし、インピーダンス整合を得ることで高速信号伝送を可能とします。

また、挿入実装タイプのコネクタを搭載する場合、高速信号伝送では、コネクタ実装面から一番離れた層に配線することでスタブによるインピーダンスの低下を抑制する方法があります。

例えば、最終的にコネクタ実装面と同じ層に配線する場合でも一旦反対側の裏層に配線し、その後スルーホールを介して表層に再接続する方法の選択である。

逆に、コネクタ実装面から配線を引き出す場合、挿入実装コネクタのリードのほとんどがスタブとなり、そこで生じるインピーダンス低下は、高速信号伝送に悪影響を及ぼします。

スルーホールのインピーダンスコントロールについては技術資料で詳しく解説していますのでそちらもご確認頂けますと幸いです。

結果

スリット跨ぎとスルーホールによる信号品質劣化の低減

信号伝送の阻害要因としてスリット跨ぎとスルーホールがあります。

この影響を少しでも緩和する為の手段をご紹介致しました。

高速差動信号伝送におけるスリット跨ぎとスルーホールに関する詳細資料、関連資料をご要望の方は、以下ダウンロードページより特別会員登録を行っていただきますようお願い申し上げます。なお、特別会員登録には一定の審査が必要ですので、ご了承いただきたくお願いいたします(弊社製品をご購入いただいてるお客様、または、それに準ずる方に限定させていただいております。)

無料ダウンロード!

【ダウンロード資料例】

- DDR3メモリバスの設計手法

- 差動伝送路の設計と信号品質

- 12G-SDIリターンロス規格合致のための基板設計手法

- IBIS-AMIモデルを用いた高速信号シミュレーション

- 10Gbps超伝送の基板設計最適化

など全70テーマ

この機会に是非ご登録ください。 ※会員登録は無料です。