プリント基板総合メーカー|RITAエレクトロニクス株式会社 > 事例紹介 > ESDイミュニティ・シミュレーション

ESDイミュニティ・シミュレーション

課題

静電気ノイズへの耐性を強くしたい。静電気ノイズ対策の検討を行いたい。

基板内へ侵入してくる静電気ノイズ、外来ノイズの影響、および、装置電源から発生し基板外へ伝達される伝導ノイズの対策は、試作開発した製品基板を使っての実機検証となっており、従来より製品開発期間短縮の妨げとなっている。

こうした実機検証の為、昨今の半導体デバイスの低電圧化、大電流化も相まって、これまで行ってきたような勘に頼った設計では対策検討も難しく、最悪の場合、設計の見直しとなり試作回数が増加してしまう。

当社のご提案

この問題を解決するため、当社ではシミュレーター(S-NAP PCB Suite/株式会社エム・イー・エル)を用いて、ESD(静電気放電)イミュニティ解析を行っている。

基本原理は次の通り。まず、多層プリント基板の層間結合を含む電磁界特性を、ヘルムホルツ方程式を基礎方程式とするFDFD(Finite-Difference Frequency-Domain)法を用いて、周波数ドメインで取得する。次に、解析で得たプリント基板の電磁界特性の外部端子やGNDにESDインパルスノイズを模した電圧を印加し、デバイスの電源-GND端子間の電位差を評価する。さらに、周波数毎に電流密度分布を確認する事で、対策の良否または原因の特定を行うものである。

なお、FDFD法とは、FDTD 法と同様の空間メッシュ分割を用いるが、周波数領域で行列方程式を解く手法であり、マクスウェルの方程式を直接、空間・時間領域での差分方程式に展開して逐次計算をすることで、電場・磁場を決定することができる計算方法である。

- 1.実験方法

-

実際に具体例をあげて説明する。半導体Aと半導体Bが搭載されたプリント基板の電磁界解析を行った。

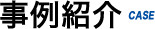

まず、プリント基板(図1)の電磁界解析を行い、基板の周波数特性を取得した。この取得した周波数特性に対して、ESDインパルスノイズを模した電圧をシミュレーション上で印加する。なお、印加電圧は、試験方法の規定にあるIEC61000-4-2により、2kVとした。電流波形とノイズスペクトラムは同図1の通り。

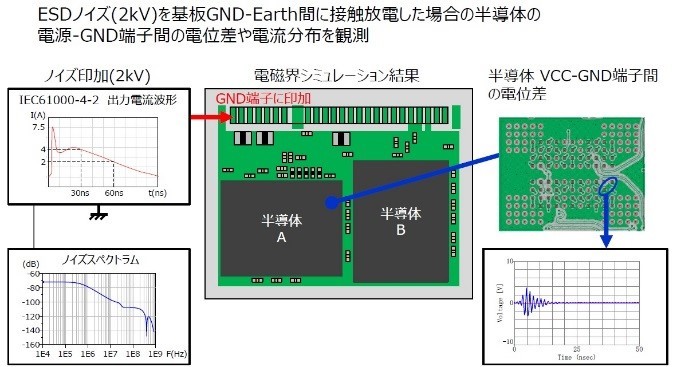

なお、シミュレーション結果の変化を観測するため、プリント基板としては、次の3通りのパターンを作成した。

(A)端子GNDとシステムGNDの間にスリットを設けた基板

(B)端子GNDとシステムGNDの一部のみスリットを設けた基板

(C)端子GNDとシステムGNDが接続されている基板(図1)ESD(放電ガン、接触放電)イミュニティ解析事例

結果

ESDイミュニティを電磁界シミュレーションで可視化するすることができた。

プリント基板の層間結合を含む電磁界特性を、電磁界シミュレーターを用いて周波数ドメインで取得し、外部端子やGNDにESDインパルスノイズを模した電圧を印加することで、デバイスの電源-GND端子間の電位差を評価する事ができ、ESDイミュニティが評価できる事が分かった。特にプリント基板のパターン設計段階でシミュレーションを実施する事で、試作回数の削減および開発期間の短縮につなげる事ができる。

無料ダウンロード!

【ダウンロード資料例】

- DDR3メモリバスの設計手法

- 差動伝送路の設計と信号品質

- 12G-SDIリターンロス規格合致のための基板設計手法

- IBIS-AMIモデルを用いた高速信号シミュレーション

- 10Gbps超伝送の基板設計最適化

など全70テーマ

この機会に是非ご登録ください。 ※会員登録は無料です。