プリント基板総合メーカー|RITAエレクトロニクス株式会社 > 技術資料 > 半導体電源起因のノイズ抑制設計

半導体電源起因のノイズ抑制設計

1.電源インピーダンス解析の重要性

半導体デバイスの高性能化にともなう大電流・低電圧化から、プリント配線板(PCB)設計でLSIへの電源供給品質の確保が課題になっています。

電源供給品質とは、チップ内部電源端子の電圧変動を動作保証する許容電圧範囲内に抑制することであり、当該部位のインプット・インピーダンス(Z11)を低減することで実現できます。また、電源系ノイズに起因したPCBからの放射ノイズの低減にはチップ内電源端子から基板端のトランスファー・インピーダンス(Z21)の低減が有効な手段の1つであることが分かっています。

2.電源インピーダンス解析手順

まず、LSIの電源モデリングを行います。

モデリングには、実際にLSIが搭載された基板をネットワークアナライザを用いて電源のインピーダンスを測定することで、LSIのDie(ダイ)のCとR、Pkg(パッケージ)のLとRを求めます。次に作成しようとするプリント基板のCADデータから、基板のネットワーク特性(Sパラメータ)を抽出します。

ここで抽出したSパラメータに先に実測したLSIのDieのCとR、PkgのLとRを電源モデルとして与え、回路シミュレーションでインピーダンス解析を実施します。3.電源インピーダンス解析結果

一例として、コア電源1.4V、I/O電源3.3VのLSIの解析結果を行いました。

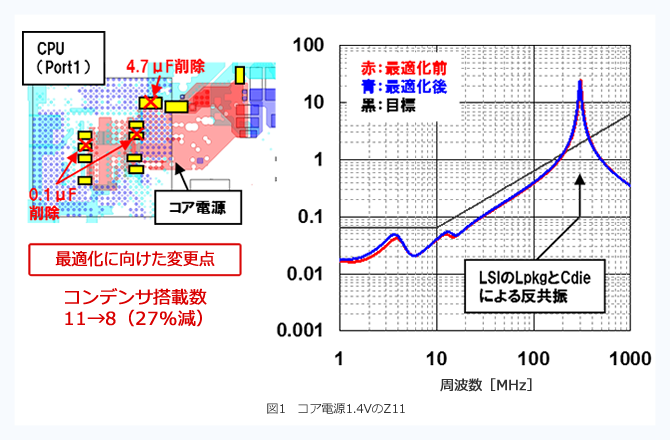

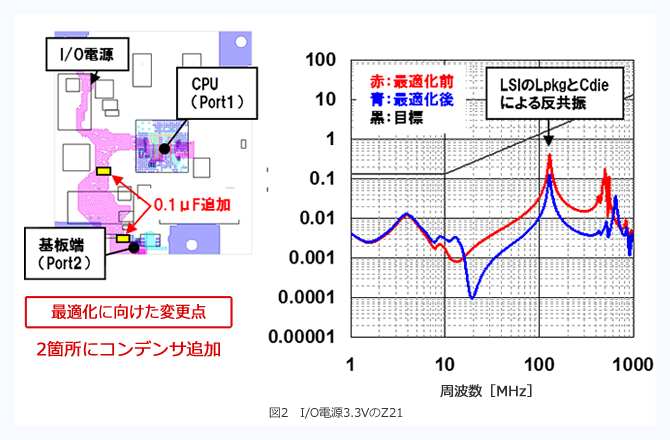

コア電源1.4VのZ11測定結果を図1に、I/O電源3.3VのZ21測定結果を図2に示します。それぞれ、何も改善を加えない状態が赤系のライン、最適化を行った状態が青系のラインで表示します。

1.4VのZ11は何も手を加えない状態で目標値をクリアーしていたため、コンデンサの削減がどの程度まで可能か検証した結果、27%削減してもZ11はほとんど変化しない結果が得られました。

3.3VのZ21は更なる低減を試み、コンデンサを2個追加することで、電源インピーダンスを下げることができます。

無料ダウンロード!

【ダウンロード資料例】

- DDR3メモリバスの設計手法

- 差動伝送路の設計と信号品質

- 12G-SDIリターンロス規格合致のための基板設計手法

- IBIS-AMIモデルを用いた高速信号シミュレーション

- 10Gbps超伝送の基板設計最適化

など全70テーマ

この機会に是非ご登録ください。 ※会員登録は無料です。