プリント基板総合メーカー|RITAエレクトロニクス株式会社 > 技術資料 > 電源・グラウンド対向部位によるバイパスコンデンサ併用効果

電源・グラウンド対向部位によるバイパスコンデンサ併用効果

1.目的

プリント基板上の半導体が動作した際、その電源端子に流れる過渡電流が原因となる放射ノイズに関し、半導体の電源ピン近傍にバイパスコンデンサを付与して対策することが一般的であるが、部品や基板配線上の制約により半導体電源ピンの近傍に十分なバイパスコンデンサが配置できないケースが発生している。

この問題に対処する方法として、プリント基板に元から配置されている電源層・グラウンド(以下、GND)層に対向するようにGND層・電源層(電源層に対してはGND層、GND層に対しては電源層)を追加して、プリント基板の内部に容量を形成する方法がある。2.実施方法①

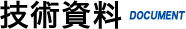

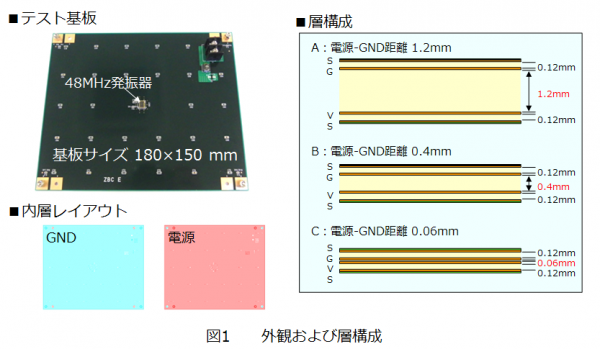

一例として、第2層がGNDプレーン、第3層が電源プレーンの4層板において、第2層と第3層の層間距離を3種類変えた基板で実測評価を行った。一般的な板厚1.6mmの4層基板は第2層のGNDプレーンと第3層の電源プレーンの距離が概ね1.2mm程度であり、これとの比較を行った。評価で用いた基板の外観および層構成は図1の通りであり、Aが第2層と第3層の層間距離1.2mm、Bが同0.4mm、Cが同0.06mmである。なお、第2層と第3層のみの層間距離を変更したため、総板厚はAが約1.6mm、Bが0.8mm、Cが0.45mmとなっている。測定評価にはプリント基板上に形成した48MHzの水晶発信器を駆動させることでノイズを発生させ、測定は3m法の電波暗室で行った。測定結果を図2の通りであり、基板A(電源とGNDの層間1.2mm)では、288MHzで約48dBμV/m、576MHzで約49dBμV/mであった。

一方で、基板B(電源とGNDの層間0.4mm)であは、それぞれ約38dBμV/m、約35dBμV/mと10dBμV/m程度低減しており、更に基板C(電源とGNDの層間0.06mm)では、観測できないレベルまで低減できた。

ただし、上記①の例では実際にプリント基板を製作する上では、板厚の制限を受けたり、配線の自由度を阻害する恐れがある。そのため、実際の製品を想定した構成を検討する必要がある。3.実施方法②

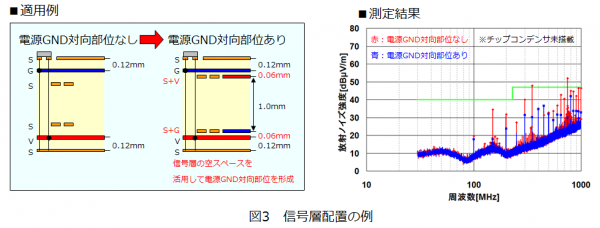

実際の製品を想定した場合、電源層とGND層を近接で配置するのは難しく、信号層の空きスペースを利用した構造を検討した。6層基板での一例の構成図とその結果を図3に示す。第3層と第4層の信号層に、それぞれ対向する電源とGNDパターンを信号線の空きスペースに配置した。

測定評価にはプリント基板上に形成した50MHzの水晶発信器および1Gbpsで駆動するシリアル・トランシーバを駆動させることでノイズ原を発生させ、測定は3m法の電波暗室で行った。その結果、対向する電源とGNDパターンを追加した場合、最大で20dBμV/m低減することができた。

無料ダウンロード!

【ダウンロード資料例】

- DDR3メモリバスの設計手法

- 差動伝送路の設計と信号品質

- 12G-SDIリターンロス規格合致のための基板設計手法

- IBIS-AMIモデルを用いた高速信号シミュレーション

- 10Gbps超伝送の基板設計最適化

など全70テーマ

この機会に是非ご登録ください。 ※会員登録は無料です。