プリント基板総合メーカー|RITAエレクトロニクス株式会社 > 技術資料 > パワー半導体搭載ボードのノイズ低減を実現する設計・解析手法

パワー半導体搭載ボードのノイズ低減を実現する設計・解析手法

- 1. はじめに

パワーエレクトロニクスの分野では、雑音端子電圧の規格合致が製品開発上の1つの問題として挙げられる。これは、パワー半導体のスイッチングに伴う急峻な電圧・電流の変化がプリント基板内を伝播し、入力端子や出力端子に出現することが原因である。

伝播するノイズは2種類あり、1つはノーマルモードノイズで、インバータなどのパワー半導体のスイッチングにより現れるノイズ成分である。もう1つはコモンモードノイズであり、先のノーマルモードが伝送線路を伝播していく過程でラインとアースとの間に発生するノイズ成分である。これらのノイズ伝播を抑えるには、基板の配線間の結合を最小にするパターン設計が必要である。

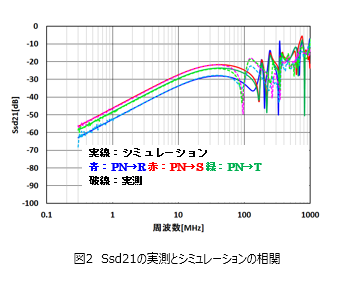

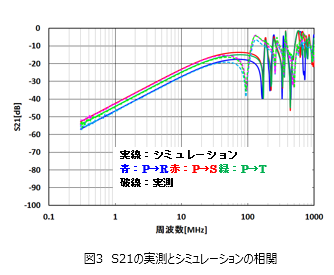

そこで、電源レイアウト間の結合量を評価するため、Ssd21およびS21というSパラメータに関する2つの表記を導入することとした。このパラメータを用いて、雑音端子電圧の低減を図る新しいパターン設計手法について検証したので報告する。

- 2. 評価基板での検証

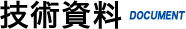

電源の配線層と配線幅の異なる2種類の4層基板(板厚1.6mm)、基板を作成した。基板の電源レイアウトを図1に示す。

基板は、電源の配線幅が全体的に太く、三相入出力電源R、S、T、U、V、W、インバータ電源端子P、Nが層間で重なるように設計したものである。

- 3. 結果と考察

基板のインバータ電源端子PNから三相入力電源端子R、S、 TへのSsd21について、実測とシミュレーションの相関を検証した。結果を図2に示す。

50MHz近傍までよく一致しており、実測とシミュレーションに相関があることがわかる。

次に、インバータ電源端子Pから入力電源端子R、 S、 TへのS21について、実測とシミュレーションの相関を検証した。結果を図3に示す。

Ssd21と同様、実測とシミュレーション結果の高い相関が確認できる。

以上より、シミュレータが出力するSパラメータの信頼性は高く、パターン設計段階におけるSsd21・S21解析により電源レイアウトの最適化が可能といえる。

無料ダウンロード!

【ダウンロード資料例】

- DDR3メモリバスの設計手法

- 差動伝送路の設計と信号品質

- 12G-SDIリターンロス規格合致のための基板設計手法

- IBIS-AMIモデルを用いた高速信号シミュレーション

- 10Gbps超伝送の基板設計最適化

など全70テーマ

この機会に是非ご登録ください。 ※会員登録は無料です。