プリント基板総合メーカー|RITAエレクトロニクス株式会社 > 技術資料 > プリント基板のファインパターン化技術

プリント基板のファインパターン化技術

- 1. はじめに

携帯端末が一般的に用いられるようになってから、電子機器の高機能化と小型化は平行して加速度的に進化して来ました。さらには、今後はウエラブル端末やIoTの普及が期待されており、より一層の高密度化が求められるようになってくると思われます。

この高密度化は半導体をはじめとする電子部品の小型化だけでなく、プリント基板の微細化により配線密度も向上してきたことも要因に上げられます。電子部品として用いられるBGAパッケージの端子ピッチは、2000年頃までは1.0mm~0.65mm程度でしたが、近年では0.4mm~0.3mmピッチのパッケージまで用いられるようになってきました。したがってこれらを実装するプリント基板にも微細(ファインパターン)化の要求がより高まってきています。

- 2. 配線の微細化(ファインパターン)要求

プリント基板の導体パターンは、銅箔や銅めっきを用いて、フォトリソグラフィーによりレジスト膜を露光、現像後、エッチングによって配線パターンを形成します。

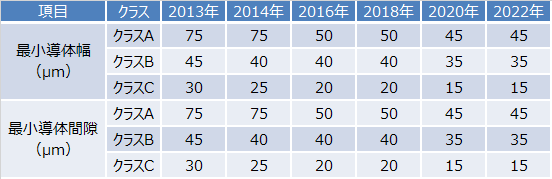

配線パターンの微細化の動向として多層プリント基板の導体寸法仕様の抜粋を表1に示します(出展:日本電子回路工業会 2014年度版プリント配線板ロードマップ)。

表1. 多層プリント基板の導体寸法仕様の抜粋

出展:日本電子回路工業会 2014年度版プリント配線板ロードマップ

比較的先端技術を有するクラスBにおいては今後、最少導体幅と最少導体間隙が35μm/35μm程度が必要となってきます。

- 3. 微細化技術

3-1. 露光精度の向上

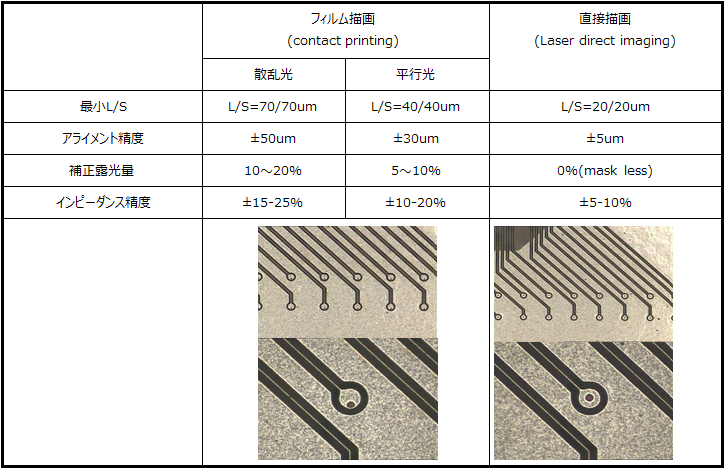

一般的なパターン露光においては、上述した通り、フォトリソグラフィーを使用します。但し、フォトフィルムを使用する事により、光の散乱が生じ、パターン精度が低下します。また、フィルムの伸縮による回路位置精度も低下します。弊社のファインパターン形成においては、フィルムを使用しない直接描画装置(Direct Imaging System)を用い露光しますので、パターン精度、再現性が向上します(図1)。

図1 フィルム描画と直接描画の精度

3-2. エッチング精度の向上

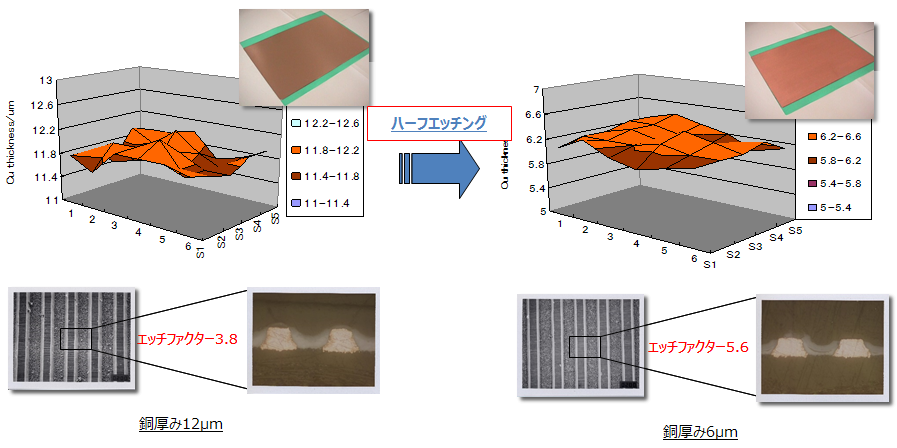

エッチング工法の一つであるサブトラクティブ法においては、エッチング媒体の厚み(エッチファクタ)が大きく影響します。この媒体には、銅厚とドライフィルムレジスト厚があり、厚いとパターン精度が低下します。弊社は、安価に基礎銅厚を薄膜処理できるハーフエッチング技術を有し、従来の基礎銅箔のマット面のまま、製造ができます(図2)。

図2. ハーフエッチングによるファインパターン化

そのため、薄膜銅箔を使用した際に起こりうる、部品リペア時・無鉛レベラー実装時のパッドリフティングなどのリスクも回避する事が出来ます。

また、標準ドライフィルムレジストの約半分の厚みのファインパターン用ドライフィルムレジストの採用により、エッチング液回りが向上し、より一層のファインパターン化が可能となっています。

- 4.まとめ

上記の技術向上により、最小ライン幅30μm、最小ライン間隙30μmでのプリント基板製造が可能となっています。

無料ダウンロード!

【ダウンロード資料例】

- DDR3メモリバスの設計手法

- 差動伝送路の設計と信号品質

- 12G-SDIリターンロス規格合致のための基板設計手法

- IBIS-AMIモデルを用いた高速信号シミュレーション

- 10Gbps超伝送の基板設計最適化

など全70テーマ

この機会に是非ご登録ください。 ※会員登録は無料です。