プリント基板総合メーカー|RITAエレクトロニクス株式会社 > 技術資料 > 伝送線路や半導体補正機能が16Gbpsシリアル伝送に及ぼす影響の実機検証

伝送線路や半導体補正機能が16Gbpsシリアル伝送に及ぼす影響の実機検証

- 1. まえがき

10Gbpsを超える信号伝送のあるプリント配線板を開発する際には、設計段階でシミュレーションを行い、伝送線路や半導体補正機能の条件を決定する。伝送線路は、プリント配線板の信号配線・ビア・パッド、ACカップリング用コンデンサ、コネクタ、ケーブル等から構成される。半導体の補正機能には、信号出力側ではプリエンファシスやデエンファシスとよばれる一部信号の強調、振幅調整、入力側ではリニアイコライザ(CTLE)や判定帰還型イコライザ(DFE)等がある。

信号伝送のシミュレーションのため、信号伝播経路については、信号配線のモデル化やケーブル等の現品の実測により送信端から受信端までの間の伝送特性を求める。半導体の信号出力と受信部にIBIS-AMIモデルを用いて受信部の波形(アイパターン)を求め、基準に合致する条件を求める方法が一般化している。ここで、受信波形を正確に求めるためには伝送経路一式についてフルウェーブの電磁界解析を行う必要があるが、それを実施するために長時間を要するため適用できる場面が限られる。16Gbpsシリアル伝送について、伝送線路と半導体補正機能の受信波形への影響を実機とシミュレーションで検証した報告は少ない。今回、特性インピーダンス不連続点のある実機を用い、16Gbpsシリアル伝送にて上記検証を行ったので、その結果を報告する。

- 2. 実験

2.1 実測

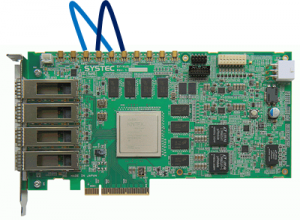

実測用ボードには㈱システック製SY-KUS-01を用いた。半導体はザイリンクス製FPGA(XCKU035-2FFVA1156C)であり、1差動対あたり16Gbpsで振幅950mVの信号(PRBS 27-1)を出力し、MMCXコネクタとこれに嵌合する同軸ケーブルを経由し、これをボードに戻して信号出力と同じFPGAで受信した。波形観測はFPGA内のIBERTとよばれる波形観測機能を用い、BER表示アイパターンで行った。プリント配線板上の16Gbps配線は表層に配置されており、配線長は出力側、受信側それぞれ90mm、絶縁層材質はMegtron-6である。ケーブルは400mm長のRG174で、両端がMMCXコネクタのものを用いた。このケーブルとコネクタについては実際の特性把握のため実測にて伝送特性を取得した。2.2 シミュレーション

まず、FPGAの信号出力端子から受信端子までの間の伝送路モデルを3種類作成した。1種目として、90mm長の基板配線はキーサイト・テクノロジー社ADSを用いてビアやパッドのない一様な配線としてモデル化し、MMCXコネクタ実装部位についてはインピーダンスが最適化されることを前提として基板配線と同じ一様とする場合であり、これを理想モデルとする。2種目として、コネクタやコンデンサ実装部の特性をTDR実測に合うように修正した場合であり、これを実測モデルとする。3種目としてADSの2.5次元モーメント法電磁界解析ソルバ(Momentum)によりビアやパッドを含むSパラメータを求めた場合であり、これを電磁界モデルとする。ケーブルについてはRG174のカタログ掲載値(最大挿入損失1.4dB@1.4dB/m、線材はAWG26等)を元に上記シミュレーションソフトでモデル化して400mmのそれを求めた。これら基板配線、ケーブル、およびコネクタとその実装部位の特性を結合した。受信端の波形シミュレーションのためには、送信部と受信部にIBIS-AMIモデルを用い、送信側は電圧を下げ、かつ、プリエンファシスを変化させ、上記3つの伝送路について受信波形を求めた。

- 3. 結果

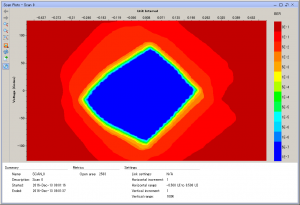

3.1 送信端~受信端の伝送特性

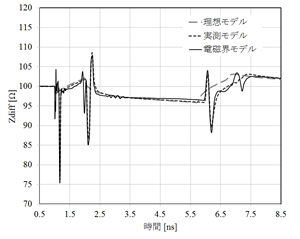

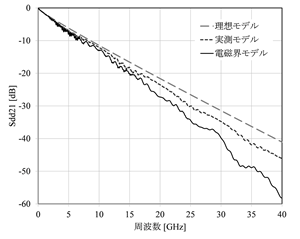

送信端から受信端までの間の伝送経路一式について、MMCXコネクタやコンデンサとその実装部位の特性インピーダンスを配線と同じにした場合(以下、理想モデルと略す)と、実測と同じ不連続点を有する場合(以下、実測モデルと略す)とビアやパッドを含む系全体を電磁界解析で求めた場合(以下、電磁界モデルと略す)の3通りについて、TDRプロファイルと伝送特性(Sdd21)を図1に示す。TDRパルスの立ち上がり時間は10%-90%で25psとした。

(a) 実測用ボード

(b) TDR特性 (c) 伝送特性(Sdd21)

図1. 実測用ボードと伝送特性

実測モデルや電磁界モデルの場合は部品実装部やビアのインピーダンス不連続が見られ、最も低いポイントで75Ωまで低下しており、これらインピーダンス不連続に起因するSdd21特性の乱れがみられるのに対して、理想モデルではこれが無いことから、理想モデルを用いたシミュレーション波形は実際よりも良くなる。

3.2 16Gbps受信波形

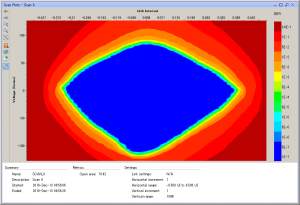

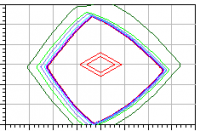

まず、半導体の補正機能として送信側プリエンファシス、受信側DFEを適用しない場合(CTLEのみ使用)の受信波形を図2に示す。

(a) 実測

(b) 理想モデル適用時 (c) 実測モデル適用時 (d) 電磁界モデル適用時

図2. プリエンファシスおよびDFEを適用しない場合の受信波形

実測にて正常な信号伝送ができており、実測モデルや電磁界配線モデルを用いたシミュレーションで同等な結果が得られている。理想モデルの場合は実測に比べてアイが空きすぎている。これは上述の影響と考えられる。

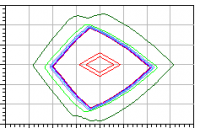

次に、送信側のみ補正機能であるプリエンファシス(12.96dB)を用いた場合の結果が図3である。このとき、実測ではリンクアップを確認できいる。

(a) 実測

(b) 理想モデル適用時 (c) 実測モデル適用時 (d) 電磁界モデル適用時

図3. 電圧変更とプリエンファシス適用時の受信波形

シミュレーションでは理想モデルの場合にBERマスクを満たせない結果となっている。これはインピーダンス不連続のない理想的な伝送路に対し、過剰に波形補正されたためと考えられる。実測モデルおよび電磁界モデル適用時に実測と同等の結果を得ている。

- 4. まとめ

基板配線とケーブルを経由した伝送線路が一様でない16Gbpsシリアル伝送において、プリエンファシスとイコライザーを適用することにより正常な信号伝送が可能になる。これは伝送線路に特性インピーダンスの不連続点のない理想モデルを用いたシミュレーションでも概して予測可能であるが、パターン設計前では理想的な設計ができない場合を想定し、不連続点を考慮したプレシミュレーションを実施することが有効である。

無料ダウンロード!

【ダウンロード資料例】

- DDR3メモリバスの設計手法

- 差動伝送路の設計と信号品質

- 12G-SDIリターンロス規格合致のための基板設計手法

- IBIS-AMIモデルを用いた高速信号シミュレーション

- 10Gbps超伝送の基板設計最適化

など全70テーマ

この機会に是非ご登録ください。 ※会員登録は無料です。