プリント基板総合メーカー|RITAエレクトロニクス株式会社 > 技術資料 > 信号伝送速度とプリント基板材質に応じた最大配線長の目安

信号伝送速度とプリント基板材質に応じた最大配線長の目安

- 1.はじめに

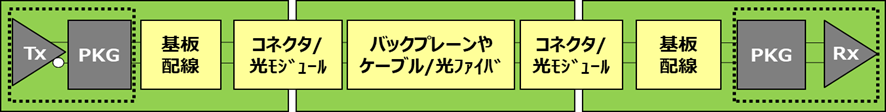

高速シリアル伝送では、複数の基板同士がコネクタやケーブルを経由して接続され、長距離伝送になるのが一般的である(図1)。

図1 高速シリアル信号伝送経路の模式図

図1 高速シリアル信号伝送経路の模式図ここで、信号出力デバイス(Tx)~受信デバイス(Rx)間の透過特性(伝送損失 Sdd21)に応じて信号が減衰するため、伝送損失ができるだけ小さい設計を行うことが重要である。

プリント基板の信号配線の伝送損失を低減させるためには、基板の材質に低損失材料を用いることが有効であるが、半導体の補正機能で一定のリカバリーが可能であるため、これを考慮した材料の選択が肝要である。

本検討は信号伝送速度に応じた伝送可能な配線長目安を把握することで、信号伝送の実現性や基材選定の判断材料を提供することを目的としている。

- 2.方法

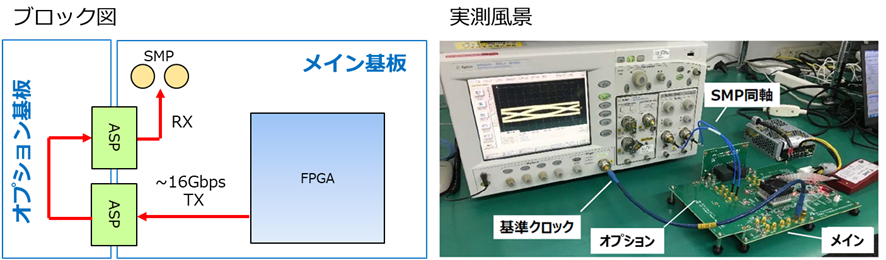

疑似ランダム信号パターン(PRBS)が出力可能なFPGAを搭載するメイン基板と、配線延長用のオプション基板から成る評価システムを用いた(図2)。

図2 評価システム

ここで、信号伝送経路を通過した後のアイパターン(信号波形を重ね書きしたもの)をサンプリングオシロスコープを用いて実測した。また、このシミュレーションも行った。基板材料には一般FR-4と低損失材料(Megtron6)を用いて、信号伝送速度は3Gbps、6Gbps、12Gbps、および16Gbpsとした。

まず、実測とシミュレーションの比較を行い、シミュレーションの妥当性について検証した。次にシミュレーションにて、速度に応じた伝送可能な配線長目安を検討した。

- 3.結果

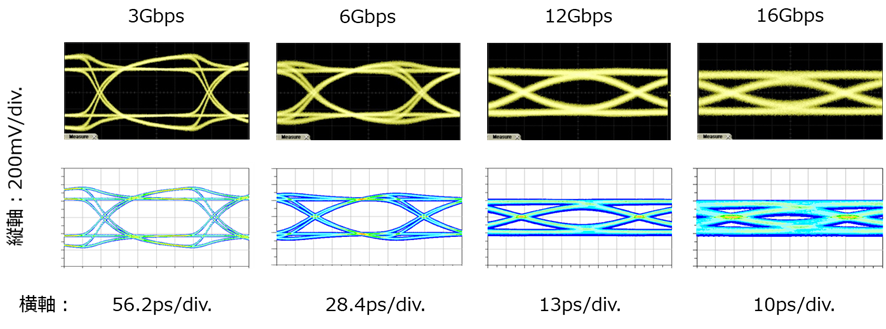

アイパターン(信号波形)の実測とシミュレーションの比較例として、図3に一般FR-4、外層配線300mmの結果を示す。

図3 アイパターン実測とシミュレーション比較例

(一般FR-4、外層配線300mm、FPGA信号出力ディエンファシス -6dB)これは、FPGAの信号出力は、波形補正機能としてディエンファシス(信号遷移直後のビットの振幅を少し小さくする機能)が-6dBの場合である。信号の受信側については波形補正機能は用いていない。

各伝送速度において、シミュレーション波形は実測波形の特徴をよく再現しており、シミュレーションの精度は高いことをを示している。信号伝送可能な配線長の検討結果例として、図4に12Gbpsにおける一般FR-4、外層配線の場合を示す。

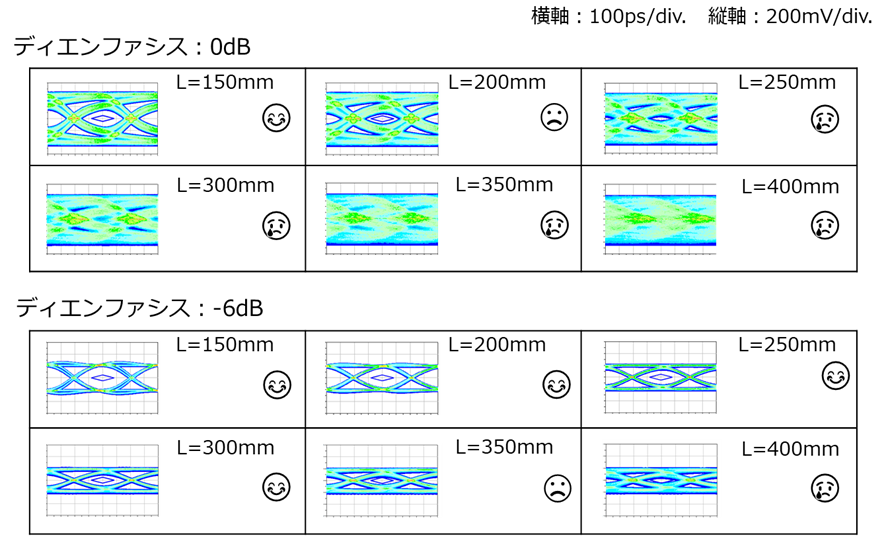

図4 信号出力側の波形補正機能(ディエンファシス)と配線長を変化させた場合の受信波形

(12Gbps、一般FR-4 外層配線)信号出力について、波形補正機能を用いない(ディエンファシス0dB)場合は200mm、これを用いる場合(デエンファシス-6dB)は350mmが最長であった。

その他材質、外層・内層、信号伝送速度、および波形補正機能を変えた場合に関する詳細資料をご要望の方は、以下ダウンロードページより会員登録を行っていただきますようお願い申し上げます。

無料ダウンロード!

【ダウンロード資料例】

- DDR3メモリバスの設計手法

- 差動伝送路の設計と信号品質

- 12G-SDIリターンロス規格合致のための基板設計手法

- IBIS-AMIモデルを用いた高速信号シミュレーション

- 10Gbps超伝送の基板設計最適化

など全70テーマ

この機会に是非ご登録ください。 ※会員登録は無料です。