プリント基板総合メーカー|RITAエレクトロニクス株式会社 > 技術資料 > 56Gbps PAM4高速伝送の実機検証|RITAエレクトロニクス株式会社

56Gbps PAM4高速伝送の実機検証

- 1.はじめに

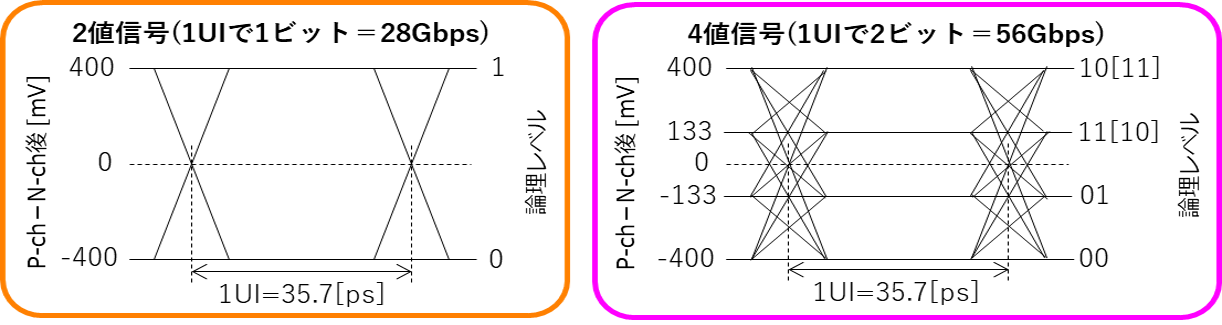

400G/800G Ethernet、PCI Express Gen6など、最新の高速インタフェースでは、従来の2値伝送の代わりに4値伝送であるPAM4(PAM4とは、Pulse Amplitude Modulation 4の略語で、4つの電圧レベルを用いる信号伝送方式)が採用されている。PAM4伝送では、電圧レベルが4値になり、振幅は小さく、信号遷移(立上り、立下り)におけるISI(Inter symbol interference, シンボル間干渉)によるジッタも課題になる(図1)。

今回、56Gbps PAM4伝送に対応するプリント基板のパターン設計ルールを検証することを目的とした伝送評価ボードを開発し、実測とシミュレーションの比較検証を行ったので報告する。

図1 2値伝送と4値伝送

図1 2値伝送と4値伝送

- 2.評価ボードと評価方法

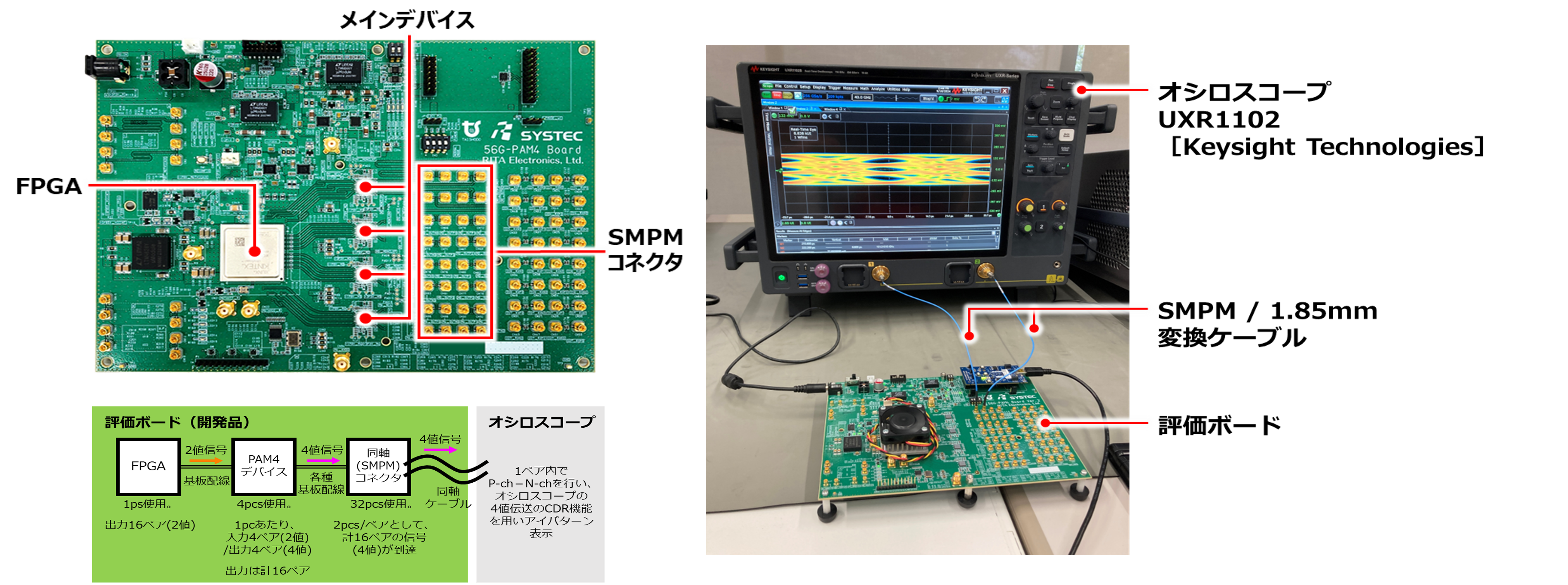

図の番号と実測環境を図の2に示す。

FPGAから28Gbpsの2値信号を出力し、PAM4デバイス(MAOM-38053B-PPR/MACOM)にて、それが56Gbpsの4値信号に変換される。4値に変換された信号は同軸コネクタ・ケーブルを経由し、高帯域リアルタイム・オシロスコープを用いてアイパターンを取得した(測定協力:キーサイト・テクノロジー株式会社)。

図2 評価ボードと実測環境

図2 評価ボードと実測環境

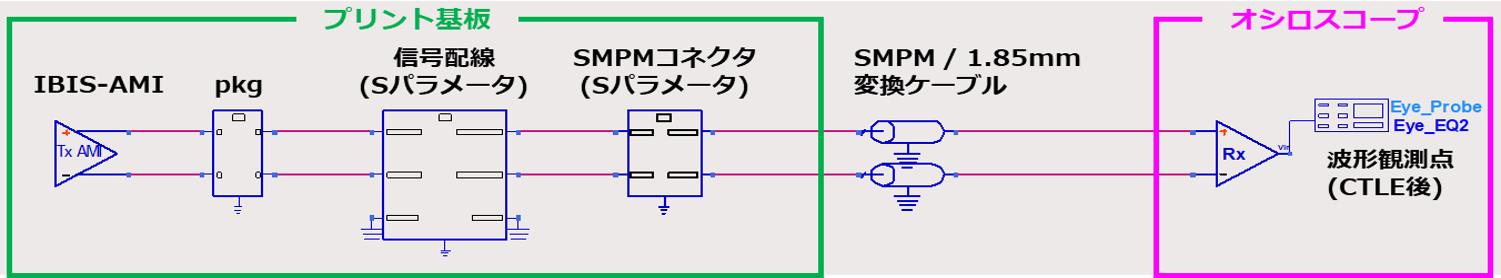

また、シミュレーションは、3次元電磁界シミュレータにてプリント基板の信号配線と同軸コネクタのモデル化を行い、回路シミュレータにてデバイスモデルと伝送線路、オシロスコープの受信モデル(CTLE)を統合し、アイパターンを取得した(図3)。

図3 シミュレーション回路

図3 シミュレーション回路

- 3.結果

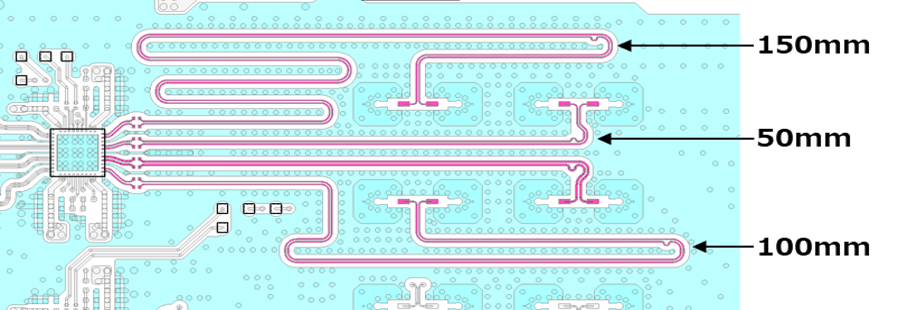

対象信号は、外層配線、差動インピーダンス100Ω、配線長が50mm、100mm、150mmの3信号(図4)である。

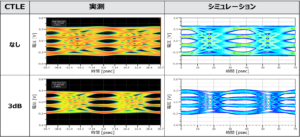

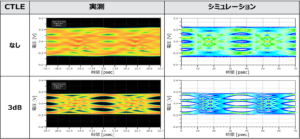

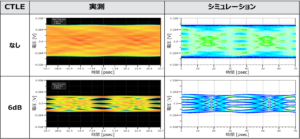

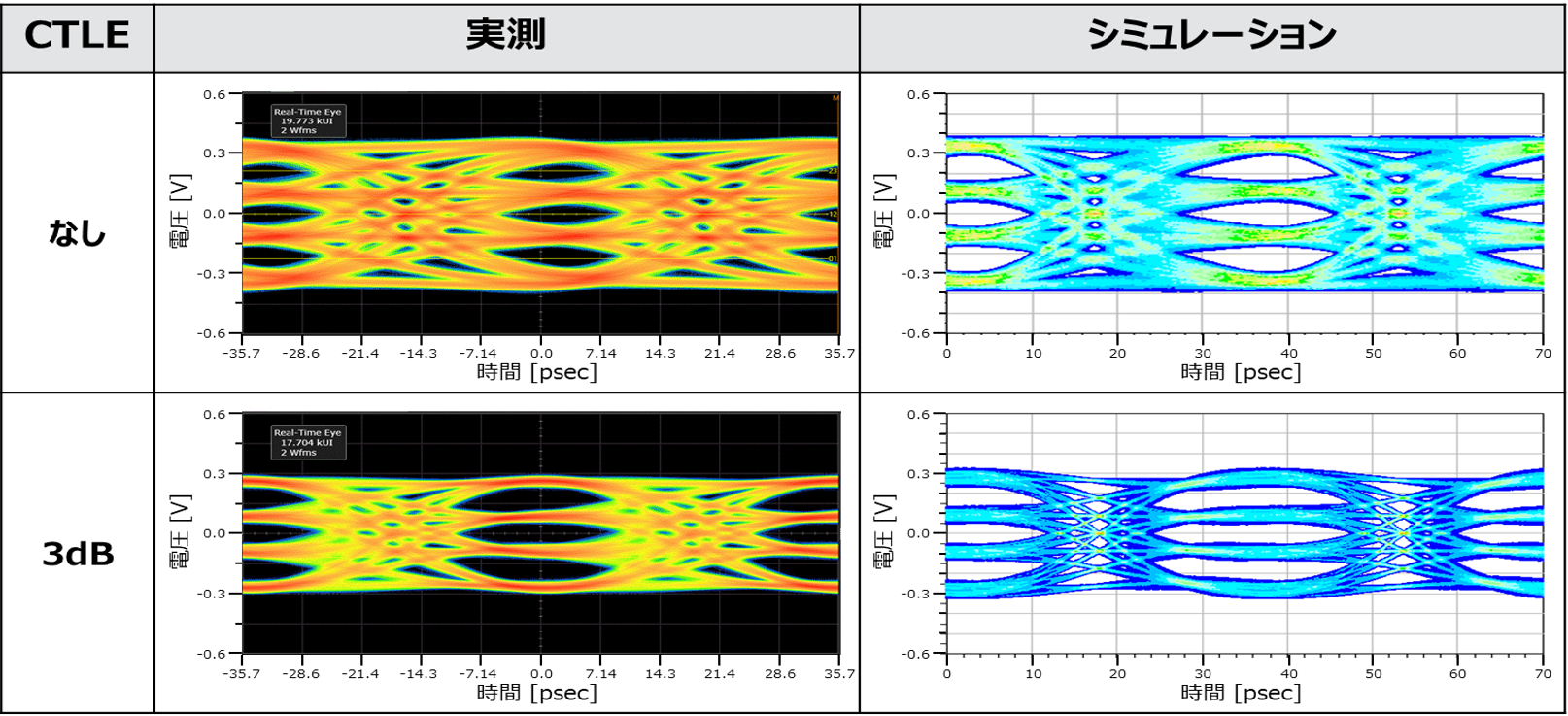

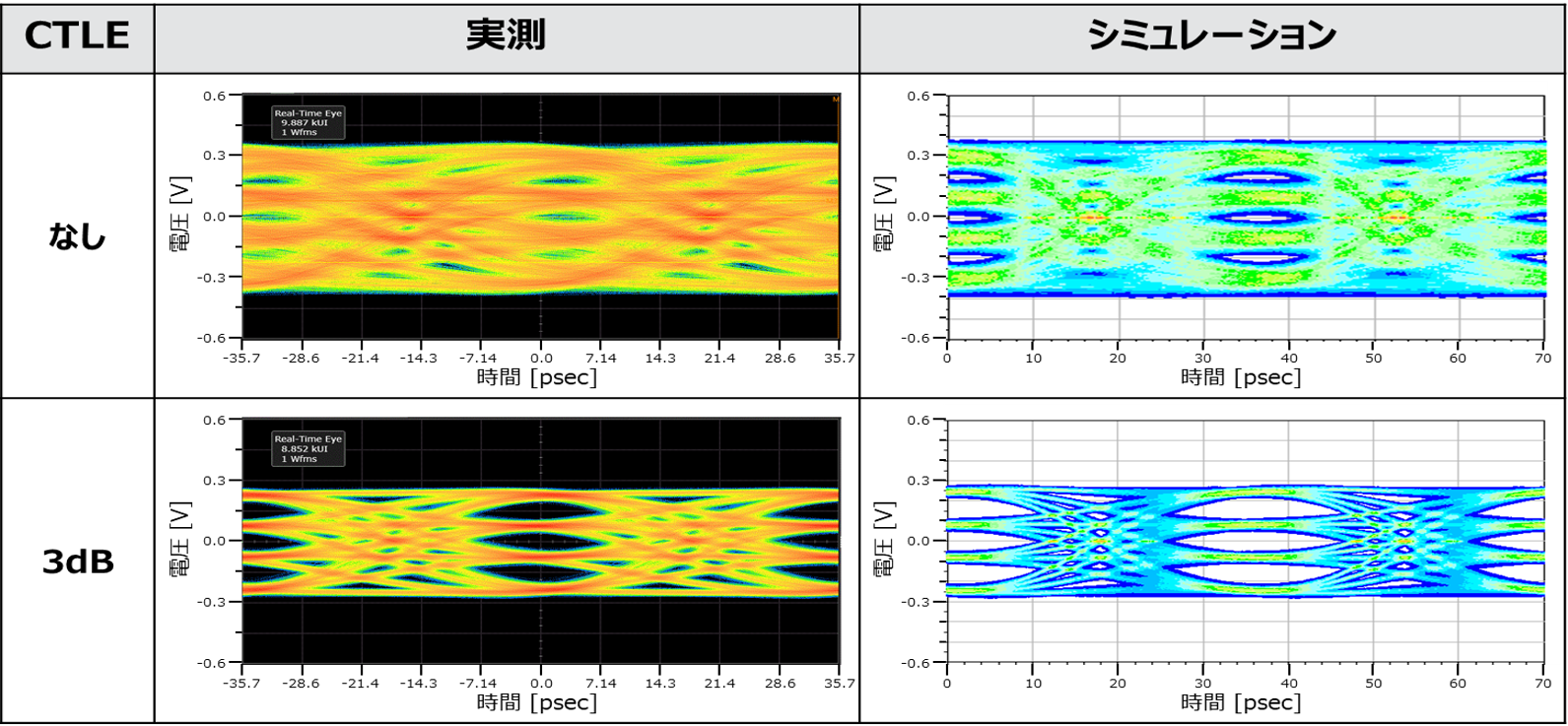

これらに対し、CTLEなし/ありの実測とシミュレーションの比較を行った。その結果を図5に示す。

図4 対象信号(配線長:50, 100, 150mm)

図4 対象信号(配線長:50, 100, 150mm)

(a)配線長50mm

(b)配線長100mm

(c)配線長150mm

図5 実測とシミュレーション比較

(a)配線長50mm

(b)配線長100mm

(c)配線長150mm

図5 実測とシミュレーション比較

実測においてCTLEなしの場合、配線長100mm以上はアイ開口が得られないが、CTLEを使用すると、配線長150mmでもアイ開口が得られた。配線長が長いほど、アイ開口が得られなくなる点は2値伝送と変わらないが、4値伝送では1つのアイの振幅が小さくなるため、より厳しくなることが懸念される。

また、シミュレーションにおいても同様な傾向が見られたが、実測と比較すると、シミュレーションの方が余裕のある結果であった。

- 4.まとめ

今回の結果から、設計段階のおけるマージン確保が重要であり、配線長はできる限り短くすることが必要である。また、この他、特性インピーダンスの不連続点を出来るだけ無くすようなパターン設計の最適化や、差動配線内の等長化といった一般的な設計ルールを遵守し、シミュレーションではデバイスの送り側や受け側の設定を最適化して、よりアイ開口が得られる条件を追求することが必要である。

無料ダウンロード!

【ダウンロード資料例】

- DDR3メモリバスの設計手法

- 差動伝送路の設計と信号品質

- 12G-SDIリターンロス規格合致のための基板設計手法

- IBIS-AMIモデルを用いた高速信号シミュレーション

- 10Gbps超伝送の基板設計最適化

など全70テーマ

この機会に是非ご登録ください。 ※会員登録は無料です。