プリント基板総合メーカー|RITAエレクトロニクス株式会社 > 製品・サービス > 製品・サービスメニュー > プリント基板 パターン設計・シミュレーション/回路設計

プリント基板 パターン設計・シミュレーション/回路設計

最新の技術を用い高速信号伝送や、ノイズ対策に対応します。

高速信号伝送やノイズ対策(EMI(放射ノイズ)・EMS(ノイズ耐性)対策)に対応したプリント配線板の回路設計、およびパターン設計とシミュレーションを行います。最新の高速DRAM・シリアル伝送対応、半導体動作にともなう電源電圧変動の抑制、およびパワー半導体搭載時の雑音端子電圧の低減まで幅広く対応します。

お見積りはこちら

プリント基板 パターン設計・シミュレーション/回路設計の対象課題

- 回路設計から一括依頼したい

- 高速信号を使う予定だが、設計方法が分からない

- ノイズ対策(EMI対策・EMS対策)をしたいがやり方が分からない

- 熱対策をしたいが、やり方がわからない

- 短納期で設計・製造がしたい

- 設計品質の向上をはかりたい

プリント基板 パターン設計・シミュレーション/回路設計の特長

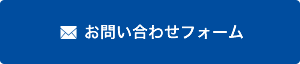

- ボード開発

-

パートナー企業とのタイアップによりデジタルからアナログまで対応

弊社高速伝送対応技術およびノイズ対策技術と、パートナー企業とのタイアップにより、ハード開発およびソフトウエア開発を行います。画像処理・高速デジタル通信・FPGA登載ボード、アナログ・無線通信・電源回路など、デジタルからアナログまで対応いたします。

- 1. 対応領域は、医療機器、分析機器、工作機器、産業ロボット、半導体製造装置、通信機器、OA機器、など多岐。

- 2. 仕様打合せにより機能設計、仕様書作成、論理設計、回路設計、FPGA設計を実施。ヒアリングを通じて仕様の策定段階から代行致します。

- 3. ファームウェア・ミドルウェア・アプリケーション開発のほか、画像処理や制御ソフトウエアの開発まで幅広い分野で最新技術をご提供致します。

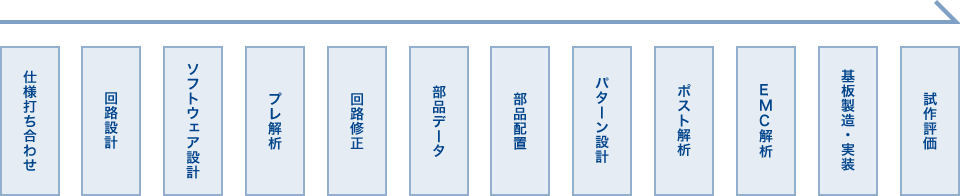

- 仕様打ち合わせ

- 回路設計

- ソフトウェア設計

- プレ解析

- 回路修正

- 部品データ

- 部品配置

- パターン設計

- ポスト解析

- EMC解析

- 基板製造・実装

- 試作評価

ボード開発のフロー

- 高速信号伝送対応

-

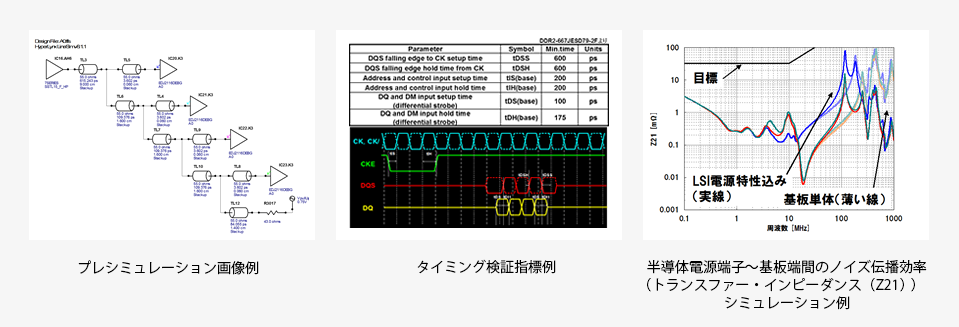

高速メモリバス~徹底したリスク検証で安定動作を実現

信号品質や要求仕様(面積、電力など)合致のため、JEDECおよび半導体メーカが公開しているデザインガイドや過去の実績を参考にして、シミュレーションで反射やクロストーク、ビアやパスコンの配置も考慮したパターン設計を行います。設計が完了すると、その設計の妥当性を検証するためにポストシミュレーションを実施します。この時、タイミングシミュレーションや同時スイッチングノイズ、およびビア間クロストークなど、回路図には現れないリスクまで検証して、安定動作を実現します。

- 1. 回路図をもとにしたパターン設計ルールの作成(プレシミュレーション)

- 2. パターン設計データに基づく波形やタイミング検証(ポストシミュレーション)

- 3. 半導体への電源供給の安定化等によるジッタの低減

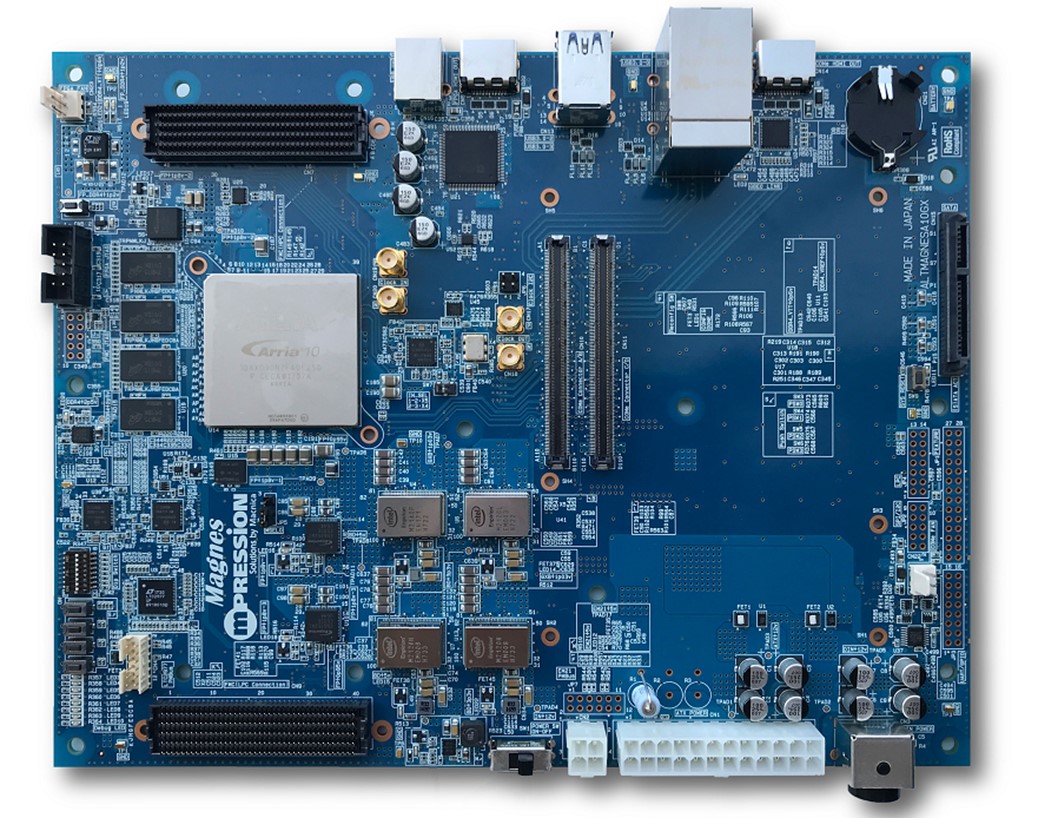

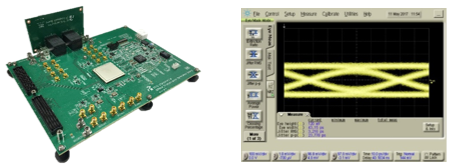

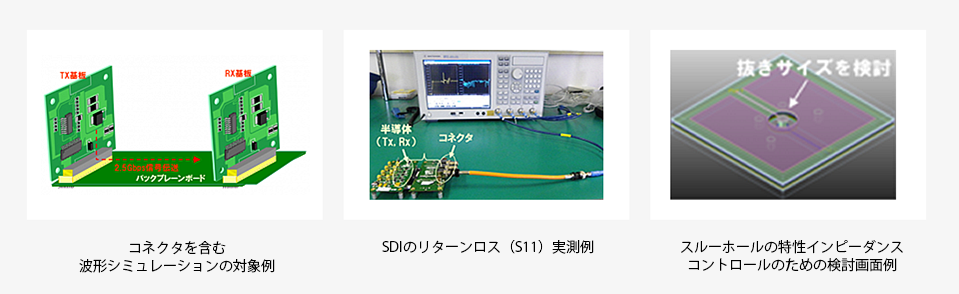

高速シリアル~反射の抑制・伝送損失の低減・ノイズ抑制~

高速シリアル伝送対応設計として、反射の抑制や伝送損失の低減、ノイズ抑制のために、 1.差動配線のインピーダンスコントロール、2.差動配線長の最短化、3.差動ペア内の配線長はできるだけそろえる、という3点を基本的なガイドラインとして基板設計を行います。

- 1. コネクタやケーブルなど伝送経路を含む波形シミュレーション

- 2. SDI(シリアル・デジタル・インタフェース)などリターンロス規格のあるインタフェースについて、コネクタ~半導体デバイス間の設計最適化による規格合致

- 3. 層間接続構造(スルーホール)を含む信号経路全体の特性インピーダンスコントロールによる信号品質の確保

- ノイズ対策

-

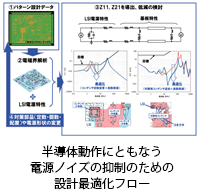

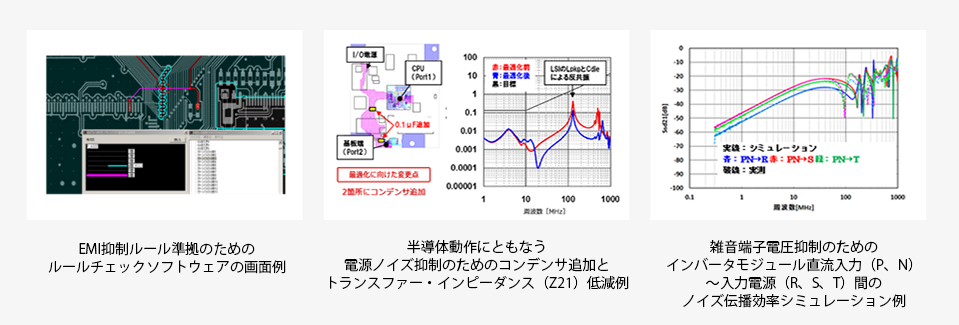

2種類のノイズ対策~EMI対策・EMS対策

ノイズ対策には2種類あります。

使用する機器からノイズをださないような対策を機器に施す=EMI対策(Electromagnetic Interference:電磁妨害)

使用する機器が外部からノイズを受けても正常に動作するよう耐ノイズ性を高める対策をする=EMS(Electromagnetic Susceptibility:電磁感受性)

これらを両立させるのが、EMC(電磁環境両立性)となります。- 1. EMI(放射ノイズ)抑制ルール準拠による放射ノイズ抑制

- 2. 半導体動作にともなう電源ノイズの抑制

- 3. パワー半導体やモジュール搭載時の雑音端子電圧の抑制

実績

| テーマ | 結果 |

|---|---|

| 回路設計・FPGA設計 | 画像測定機器、放送・通信機器 |

| 高速信号伝送設計 | 56Gbps/PAM4、28Gbps、14Gbps、10Gbps、PCI-Express Gen3、12G-SDI、USB3.0、SATAⅢ |

| ノイズ対策設計 | VCCI、CISPR11、CISPR22、FCC |

| パワー回路・アナログ回路対応設計 | 雑音端子電圧低減 |

| 熱対策設計 | 半導体発熱温度低減 |

| 短納期設計 | 同時並行設計、休日対応 |

関連事例

- FPGAボードの電源設計

ー最適な設計方法を解説 -

FPGAのロジック設計を基板が完成後に行ったことで、問題が後から顕在化し、基板を改版しなければならないことがあります。この手戻りを減らすため、ロジック設計と回路設計が協調設計を行うことで電源をはじめとして各設計、各動作を最適化できます。さらにPI解析、SI解析を必要に応じて実施することで、さらに品質を高めることが可能です。

- 設計

- 量産製造を見据えたプリント基板設計

-

量産性を考慮せずに設計してしまったことにより、プリント基板設計の改版を行う事があります。この手戻りを減らすため、当社グループではプリント基板設計、基板製造、部品実装をグループ内で連携し対応しています。基板設計~部品実装をご一括でご指示いただくことで、量産製造(部品実装)を見据えた基板設計を行います。

- 設計

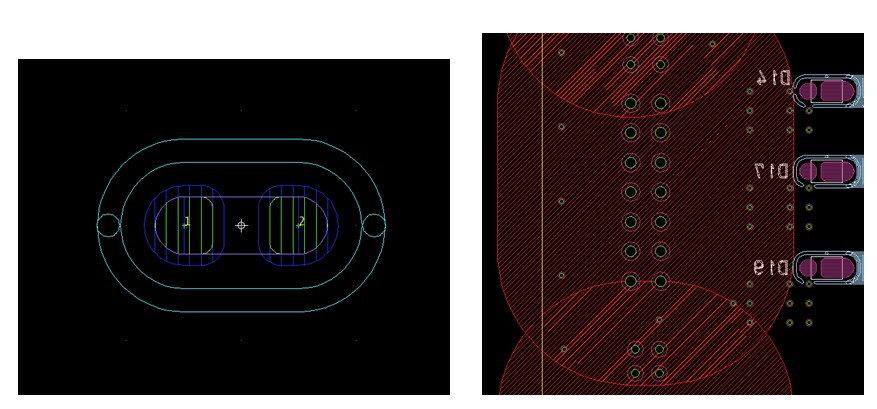

- ESDイミュニティ・シミュレーション

-

プリント基板の電磁界特性を電磁界シミュレーターを用いて取得し、外部端子やGNDにESDインパルスノイズを模した電圧を印加することで、デバイスの電源-GND端子間の電位差を評価する事ができる。特にプリント基板のパターン設計段階でシミュレーションを実施する事で、試作回数の削減および開発期間の短縮につなげる事ができる。

- 設計

- FPGA設計サービス

-

経験のないFPGA使用への不安、また開発リソース不足から外部委託の需要が増えています。16Gbpsシリアル伝送ボードの開発には、従来デバイスでは対応出来ず最新デバイスを使う必要があり、設計実績のある先へ委託することでリソースを他に回すことができました。結果として、ボード評価に注力できるようになりました。

- 設計

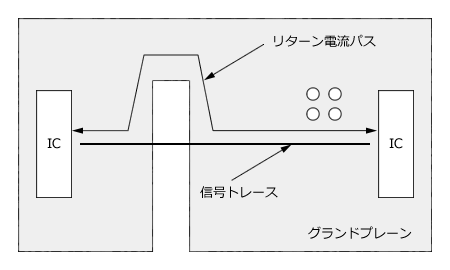

- 信号線の放射ノイズ対策

ーパターン設計によるノイズ低減 -

信号速度の高速化に伴い、プリント基板の配線パターンに高周波の電流が流れると不要輻射となることがあります。高密度・高多層のプリント基板になってくるとリターン経路を人手により確認しなが設計するのは、かなり困難となります。弊社ではEMI抑制設計支援ツール(NEC製DEMITASNX)を活用し、最適パターン設計を行います。

- ノイズ対策

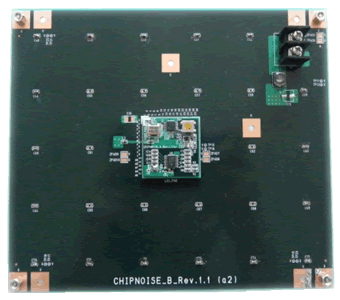

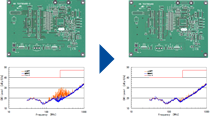

- プリント基板の電源ノイズ対策

-

電子機器の高速化と大電流化によりLSIから発生した電源ノイズが不要輻射の原因になることがあります。「層構成を変更しGNDを強化する方法」または「電源層をパターン化しノイズ拡散を抑制する方法」により、144MHzと388MHzにおいて、それぞれ15dBμV程度ノイズを低減することが出来ました。

- ノイズ対策

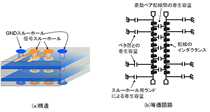

- 基板内差動配線のスルーホールとスリット跨ぎによる信号伝送劣化対策

-

プリント基板上に生じ差動信号配線の阻害要因であるリファレンス

プレーンに生じたスリット跨ぎやスルーホールを通過場合の信号品 質への悪影響を低減する為の工夫や手段を紹介しています。 - 高速信号伝送

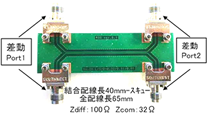

- 高速差動信号伝送におけるプリント基板の伝送特性への影響

-

差動伝送のペア配線は、トータル配線長を揃えようと短い配線側で余長処理を行います。

しかし同じ長さでも、結合配線までの配線や結合配線内といった個別箇所単位でスキューが生じているケースがほとんどです。

そのような場合、伝送特性にどのような影響が生じるかを実験結果からまとめました。

- 高速信号伝送

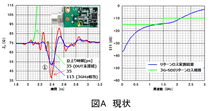

- 高速差動配線ペア内結合と伝送損失

-

同一配線層に結合度の違う3種類の差動配線を準備し、伝送損失の測定をしました。

結合度に差異がある事から、配線幅に違いが生じてます。

伝送損失の低減を望む場合、配線幅の太い(結合が希薄)配線が最善のように考えられていますが・・・

- 高速信号伝送

- SDIリターンロス規格合致のための設計ソリューション

-

SDI(シリアル・デジタル・インタフェース)が搭載されるプリント配線板を開発する際には、リターンロス規格への合致が課題となります。

このために、スペックアウトした現品を対象とした、実測とシミュレーションによる具体的なプリント配線板の改版指針の決定方法の事例を紹介します。

- 高速シリアル伝送

当社のご紹介

保有設備

| パターン設計用CAD | CR8000DF,CR5000BD,CR5000PWS (図研),Allegro PCB (Cadence),Xpedition (Mentor) |

|---|---|

| シミュレーションソフト・

ルールチェックソフト |

HyperLynx SI (Mentor),Femtet (Murata Software),ADS/Momentum (Keysight),HFSS,

SIwave (ANSYS),S-NAP PCB Suite (エム・イー・エル),DEMITASNX (NEC) |

| 品質チェックソフト | Valor NPI (Mentor),DFM Center (図研) |

| 検図用ビューワーソフト | XDF Viewer (図研) |

よくある質問

パターン設計およびプリント基板製造の基準を教えてください。

当社では、「プリント配線板 設計・製品 標準仕様書」という標準仕様を纏めた物を用意しております。ご要望がありましたら、お渡し可能ですので、お問い合わせをお願いします。

なお、抜粋の「設計標準仕様書」は、会員用のダウンロード資料としてダウンロード可能ですので、会員登録の上、ダウンロードいただいても結構です。ただし、特別会員向けとなりますので、登録時に簡単な審査がございます。

回路設計からの依頼は可能でしょうか?

可能です。要求仕様書があれば、そちらをご提供いただきたくお願いいたします。

回路設計する際のCADは何を使っていますでしょうか?

CR5000SDやOrCADが主力CADとなります。

FPGA設計を依頼することは可能でしょうか?

可能です。Altera、Xilinxどちらも可能です。RTLの言語は、VerilogHDL、VHDLで対応しています。

パターン設計のCADは何を使っていますでしょうか?

CR5000BD(図研)、CR5000PWS(図研)、Allegro(Cadence)が主力CADです。

パターン設計を依頼する際に必要なデータを教えてください。

回路図、外形図(公差含む)、ネットリスト、部品表、設計指示書、などが必要となります。

パターン設計を依頼する際に必要なネットリストの種類を教えてください。

Accel_Ascii、Allegro、Protel、Telesis、など約40種類のフォーマットに対応しています。

対応可能なシミュレーションの内容を教えてください。

伝送路解析、ノイズ解析、熱解析などが可能です。それ以外も内容によっては対応可能ですので、お問合せをお願いいたします。

シミュレーションツールは何を使っていますでしょうか?

HyperLynx SI (Mentor) ADS (Keysight) Microwave Office (AWR) HSPICE (Synopsys) SIwave (ANSYS) DEMITASNX (NEC)

伝送線路系のシミュレーションに必要な情報を教えてください。

回路図、部品表、対象信号、対象デバイスのモデル(IBIS、SPICE)が必要となります。

関連事例

- FPGAボードの電源設計

ー最適な設計方法を解説 -

FPGAのロジック設計を基板が完成後に行ったことで、問題が後から顕在化し、基板を改版しなければならないことがあります。この手戻りを減らすため、ロジック設計と回路設計が協調設計を行うことで電源をはじめとして各設計、各動作を最適化できます。さらにPI解析、SI解析を必要に応じて実施することで、さらに品質を高めることが可能です。

- 設計

- 量産製造を見据えたプリント基板設計

-

量産性を考慮せずに設計してしまったことにより、プリント基板設計の改版を行う事があります。この手戻りを減らすため、当社グループではプリント基板設計、基板製造、部品実装をグループ内で連携し対応しています。基板設計~部品実装をご一括でご指示いただくことで、量産製造(部品実装)を見据えた基板設計を行います。

- 設計

- ESDイミュニティ・シミュレーション

-

プリント基板の電磁界特性を電磁界シミュレーターを用いて取得し、外部端子やGNDにESDインパルスノイズを模した電圧を印加することで、デバイスの電源-GND端子間の電位差を評価する事ができる。特にプリント基板のパターン設計段階でシミュレーションを実施する事で、試作回数の削減および開発期間の短縮につなげる事ができる。

- 設計

- FPGA設計サービス

-

経験のないFPGA使用への不安、また開発リソース不足から外部委託の需要が増えています。16Gbpsシリアル伝送ボードの開発には、従来デバイスでは対応出来ず最新デバイスを使う必要があり、設計実績のある先へ委託することでリソースを他に回すことができました。結果として、ボード評価に注力できるようになりました。

- 設計

- 信号線の放射ノイズ対策

ーパターン設計によるノイズ低減 -

信号速度の高速化に伴い、プリント基板の配線パターンに高周波の電流が流れると不要輻射となることがあります。高密度・高多層のプリント基板になってくるとリターン経路を人手により確認しなが設計するのは、かなり困難となります。弊社ではEMI抑制設計支援ツール(NEC製DEMITASNX)を活用し、最適パターン設計を行います。

- ノイズ対策

- プリント基板の電源ノイズ対策

-

電子機器の高速化と大電流化によりLSIから発生した電源ノイズが不要輻射の原因になることがあります。「層構成を変更しGNDを強化する方法」または「電源層をパターン化しノイズ拡散を抑制する方法」により、144MHzと388MHzにおいて、それぞれ15dBμV程度ノイズを低減することが出来ました。

- ノイズ対策

- 基板内差動配線のスルーホールとスリット跨ぎによる信号伝送劣化対策

-

プリント基板上に生じ差動信号配線の阻害要因であるリファレンス

プレーンに生じたスリット跨ぎやスルーホールを通過場合の信号品 質への悪影響を低減する為の工夫や手段を紹介しています。 - 高速信号伝送

- 高速差動信号伝送におけるプリント基板の伝送特性への影響

-

差動伝送のペア配線は、トータル配線長を揃えようと短い配線側で余長処理を行います。

しかし同じ長さでも、結合配線までの配線や結合配線内といった個別箇所単位でスキューが生じているケースがほとんどです。

そのような場合、伝送特性にどのような影響が生じるかを実験結果からまとめました。

- 高速信号伝送

- 高速差動配線ペア内結合と伝送損失

-

同一配線層に結合度の違う3種類の差動配線を準備し、伝送損失の測定をしました。

結合度に差異がある事から、配線幅に違いが生じてます。

伝送損失の低減を望む場合、配線幅の太い(結合が希薄)配線が最善のように考えられていますが・・・

- 高速信号伝送

- SDIリターンロス規格合致のための設計ソリューション

-

SDI(シリアル・デジタル・インタフェース)が搭載されるプリント配線板を開発する際には、リターンロス規格への合致が課題となります。

このために、スペックアウトした現品を対象とした、実測とシミュレーションによる具体的なプリント配線板の改版指針の決定方法の事例を紹介します。

- 高速シリアル伝送